# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE UNIVERSITÉ IBN-KHALDOUN TIARET

FACULTÉ DES SCIENCES APPLIQUEES

DÉPARTEMENT DES SCIENCES ET TECHNOLOGIE

# Polycopié de TP

# LOGIQUE COMBINATOIRE ET SEQUENTIELLE

Préparé par : Dr. Imane GHLIB

**Promotion:**

Licence Électronique Expertisé par :

Licence2 Électronique Dr. BELARBI Mustapha

Licence2 Électromécanique Dr. BELHADJI Youcef

Licence2 Automatique

Semestre: 03

Année universitaire: 2023/2024

# Table des matières

| Avant- propos                                                           | I   |

|-------------------------------------------------------------------------|-----|

| Le déroulement d'un TP                                                  | III |

| TP N°1 : Initiation sur les Portes Logiques                             | 4   |

| But du TP                                                               | 4   |

| Rappel théorique                                                        | 4   |

| Brève présentation du logiciel ISIS- PROTEUS                            | 5   |

| Travail à faire                                                         | 7   |

| TP N°2 : Etude et réalisation des fonctions logiques                    | 9   |

| BUT DU TP :                                                             | 9   |

| RAPPEL THEORIQUE                                                        | 9   |

| Partie expérimentale                                                    | 11  |

| Travail à faire                                                         | 12  |

| Questions                                                               |     |

| TP N°3 : Etude et réalisation d'un Multiplexeur par des Portes Logiques | 16  |

| BUT DU TP :                                                             | 16  |

| RAPPEL THEORIQUE                                                        |     |

| Branchage des circuits intégrés utilisés                                |     |

| Le montage d'un multiplexeur 2 à 1                                      | 21  |

| Le montage d'un multiplexeur 4 à 1                                      | 21  |

| Le montage d'un multiplexeur 1 à 4                                      |     |

| Questions                                                               | 22  |

| TP N° 4 : Etude et réalisation d'un circuit combinatoire arithmétique   | 23  |

| BUT DU TP:                                                              | 23  |

| RAPPEL THEORIQUE                                                        | 23  |

| L'additionneur                                                          | 23  |

| Additionneur en circuit intégré                                         | 24  |

| Le soustracteur                                                         | 24  |

| Créer des sous-circuits                                                 |     |

| Branchage des circuits intégrés utilisés                                | 26  |

| TP N° 5 : Etude et réalisation d'un circuit séquentiel                  | 27  |

| BUT DU TP:                                                              | 27  |

| Logique séquentielle :                                                  | 27  |

| Les bascules                                                            | 27  |

| Les compteurs                                                           | 29  |

| Bibliographie                                                           | 30  |

# Table des figures

# $TP\ N^\circ 1$ : Initiation sur les Portes Logiques

| Figure 1. 1 La porte logique « ET »                   | 5                   |

|-------------------------------------------------------|---------------------|

| Figure 1. 3 La porte logique ET 74LS08                |                     |

| TP N°2 : Etude et réalisation des fonctions           | logiques            |

| Figure 2. 1 Le circuit intégré logique                |                     |

| Figure 2. 2 Le branchement d'un circuit intégré       |                     |

| Figure 2. 3 La plaque d'essai                         |                     |

| Figure 2. 4 la LED                                    | 12                  |

| TP N°3 : Etude et réalisation d'un Multiplexeur par d | les Portes Logiques |

| Figure 3. 1 Multiplexeur                              |                     |

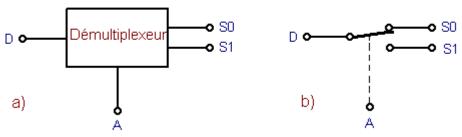

| Figure 3. 2 Démultiplexeur                            |                     |

| Figure 3. 3 Démultiplexeur 1 à 2                      | 17                  |

| Figure 3. 4 Démultiplexeur 1 à 4                      |                     |

| Figure 3. 5 Multiplexeur 74157                        |                     |

| Figure 3. 6 Multiplexeur 74153                        |                     |

| Figure 3. 7 Démultiplexeurs 74LS139                   |                     |

| Figure 3. 8 Le brochage de démultiplexeurs 74LS139    | 20                  |

| TP N° 4 : Etude et réalisation d'un circuit combinat  | oire arithmétique   |

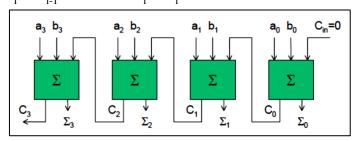

| Figure 4. 1 Principe de l'addition sur 4 bits         | 23                  |

| Figure 4. 2 Architecture de l'additionneur            | 24                  |

| Figure 4. 3 Le sous-circuit                           | 25                  |

| Figure 4. 4 La feuille enfant                         | 26                  |

| Figure 4. 5 Additionneur 74LS83                       | 26                  |

| TP N° 5 : Etude et réalisation d'un circu             | it séquentiel       |

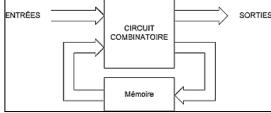

| Figure 5. 1 Circuit séquentiel                        | 27                  |

| Figure 5. 2 Bascule RS.                               | 27                  |

| Figure 5. 3 Bascule RS NOR                            | 27                  |

| Figure 5. 4 Bascule RS NAND                           | 28                  |

| Figure 5. 5 Bascule JK.                               | 28                  |

# **Avant- propos**

Ce document a été élaboré à partir de trois années d'enseignement des travaux pratiques « TP Logique combinatoire et séquentielle » destinés aux étudiants de 2<sup>ième</sup> année spécialité génie électrique du premier cycle au niveau de département génie électrique de l'université de Tiaret. Ce document a été développé en accord avec le canevas officiel établi par le ministère de l'Enseignement Supérieur et de la Recherche Scientifique

#### Contenue du module :

TP N°1: Technologie des circuits intégrés TTL et CMOS.

Apprendre et tester les différentes portes logiques

TP N°2 : Etude et réalisation de fonctions logiques combinatoires usuelles

Exemple : les circuits d'aiguillage (MUX et/ou DMUX), les circuits de codage et de décodage,

TP N°3: Etude et réalisation d'un circuit combinatoire arithmétique

Réalisation d'un circuit additionneur et /ou soustracteur de 2 nombres binaires à 4 bits.

#### TP N°4: Etude et réalisation d'un circuit combinatoire logique

Réalisation d'une fonction logique à l'aide de portes logiques. Exemple un afficheur à 7 segments et/ou un générateur du complément à 2 d'un nombre à 4 bits et/ou générateur du code de Gray à 4 bits.

#### TP N°5 : Etude et réalisation de circuits compteurs

Circuits compteurs asynchrones incomplets à l'aide de bascules, Circuits compteurs synchrones à cycle irrégulier à l'aide de bascules

Pendant les travaux pratiques de logique combinatoire et séquentielle, les étudiants peuvent développer des compétences de plusieurs manières :

Compréhension des concepts théoriques: Les travaux pratiques débutent souvent par une partie théorique qui explique les concepts de base ainsi que les principes fondamentaux de la logique combinatoire et séquentielle. Les étudiants doivent comprendre ces concepts pour pouvoir les appliquer correctement dans les applications pratiques.

Analyse et conception de circuits: Les étudiants sont généralement amenés à concevoir des circuits combinatoires et séquentiels en utilisant des circuits intégrés pour réaliser des portes logiques, des bascules, des compteurs, etc.

**Utilisation d'outils de simulation :** certaines travaux pratiques impliquent l'utilisation de logiciels de simulation de circuits électroniques généralement « Proteus ». Les étudiants apprennent à utiliser ces outils pour vérifier le comportement de leurs conceptions et comprendre les interactions entre les différents composants.

Les fiches techniques ont été élaborées dans un ordre séquentiel correspondant au déroulement du TP. Cette organisation vise à faciliter la prise de résultats et à permettre aux étudiants de noter les observations importantes et les éventuelles remarques.

I

Nous encourageons activement les étudiants à participer activement aux expériences, à poser des questions et à discuter des résultats obtenus. Cette approche interactive favorise une meilleure compréhension des concepts et prépare les étudiants à appliquer leurs connaissances dans des situations pratiques.

Ce polycopié a été élaboré en se basant sur des références renommées dans le domaine de l'électronique, assurant ainsi une qualité et une pertinence des contenus. Les références utilisées comprennent des ouvrages de spécialistes reconnus et des ressources académiques largement acceptées [1-3].

#### Objectifs de l'enseignement

Consolider les connaissances acquises pendant le cours de la matière "Logique Combinatoire et Séquentielle" par des travaux pratiques pour mieux comprendre et assimiler le contenu de cette matière.

#### **Public cible**

Ces TP sont destinés aux étudiants de  $2^{i\text{ème}}$  année licence LMD en science technique. Génie électrique.

II

## Le déroulement d'un TP

Le déroulement d'un TP (Travaux Pratiques) en électronique peut varier en fonction des objectifs spécifiques du TP et du niveau d'études. Cependant, voici un déroulement général que vous pourriez suivre pour le TP d'électronique :

#### 1. Introduction et Objectifs :

- Présentation des objectifs du TP et des concepts à étudier.

- Explication de l'équipement et des composants utilisés.

#### 2. Théorie:

- Revue des concepts théoriques pertinents.

- Présentation des principes de base liés au TP.

#### 3. Préparation du Matériel :

- Distribution des composants, des câbles et des instruments.

- Vérification du bon fonctionnement des appareils de mesure.

#### 4. Montage du Circuit :

- Instruction sur le montage du circuit en suivant un schéma donné.

- Application des principes théoriques à la configuration pratique.

# 5. Mesures et Expérimentation :

- Utilisation d'instruments de mesure tels que les oscilloscopes, les multimètres, etc.

- Réalisation de mesures pour vérifier les caractéristiques du circuit.

#### 6. Analyse des Résultats :

- Interprétation des résultats obtenus par rapport aux attentes théoriques.

- Discussion sur les sources d'erreurs possibles.

#### 7. Questions et Discussions :

- Réponses aux questions des étudiants.

- Discussions sur les observations et les résultats.

#### 8. Rapport ou Compte Rendu:

• Rédaction d'un rapport décrivant le TP, les résultats obtenus et les analyses effectuées.

Ш

• Soumission du rapport pour évaluation.

#### 9. Conclusion:

- Récapitulation des principales conclusions tirées du TP.

- Discussion sur les applications pratiques des concepts étudiés.

# **TP N°1 : Initiation sur les Portes Logiques**

#### But du TP.

Les objectifs de ce TP sont :

✓ Comprendre et tester le fonctionnement des portes logiques de base : AND, OR

Universal: NAND, NOR Avancés: XOR, XNOR

- ✓ Maitriser les opérations d'Algèbre de Boole et ses propriétés.

- ✓ Familiariser avec le logiciel ISIS Proteus afin de créer, de tester et de valider des logigrammes.

# Rappel théorique

# • Fonctions logiques de base

Les opérations logiques sont en informatique aussi courantes si pas plus que les opérations

arithmétiques. La logique combinatoire tout comme l'arithmétique repose sur quelques opérations élémentaires.

- ✓ En arithmétique, ces opérations sont l'addition, la soustraction, la multiplication et la division (+, -, \*, /). Il est possible à partir de là d'imaginer toutes les autres opérations telles que les exposants, les racines, les logarithmes etc.

- ✓ En logique, les opérations fondamentales sont le NON, le ET et le OU.

# • Les variables logiques

Pour comprendre le principe de la conception des portes logiques des interrupteurs sont utilisés pour modéliser les variables d'entrées et des lampes électriques pour les sorties. Cette modélisation nous permet de comprendre le fonctionnement et la relation entre l'algèbre booléenne et circuits logiques numériques.

- -Un interrupteur peut être soit fermée (*1 logique*), soit ouvert (*0 logique*). Il possède donc 2 états possibles de fonctionnement.

- -Une lampe possède également 2 états possibles de fonctionnement qui sont éteinte (*0 logique*) ou allumée (*1 logique*)

Alors, une variable logique est une grandeur qui ne peut prendre que deux états logiques. On les symbolise par 0 ou 1.

Pour décrire le fonctionnement d'un système en cherchant l'état de la sortie pour toutes les combinaisons possibles des entrées, on utilisera « La table de vérité »

4

plus simples sont appelés portes logiques. Ils sont la base de la logique mathématique qui effectue les opérations à l'intérieur du processeur, c'est la base de tous les calculs internes du

Les circuits combinatoires les

#### • Table de Vérité :

Une table de vérité est un tableau qui montre toutes les combinaisons possibles d'entrées pour une fonction booléenne donnée, ainsi que la sortie correspondante pour chaque combinaison. Pour une fonction booléenne avec n variables d'entrée, il y aura  $2^n$  lignes dans la table de vérité, chaque ligne représentant une combinaison unique de valeurs d'entrée.

# • La porte logique « ET » :

En termes d'algèbre booléenne, cette expression est celle de la fonction ET qui est désignée par un point unique (.) Entre les variables en donnant l'expression booléenne de :

S = A.B

La fonction ET « **AND** » est appelée fonction de multiplication d'algèbre *logique* « *logique* « *logique* » .

Figure 1. 1 La porte logique « ET »

| Table de vérité |   |   |

|-----------------|---|---|

| A               | В | S |

| 0               | 0 | 0 |

| 0               | 1 | 0 |

| 1               | 0 | 0 |

| 1               | 1 | 1 |

# • La porte logique « OU » :

En termes d'algèbre booléenne, l'expression de la fonction OU est désignée par un signe plus (+) entre les variables en donnant l'expression booléenne de :

$$S = A + B$$

.

La fonction OU « OR » est appelée la fonction d'addition logique d'algèbre booléenne.

Figure 1. 2 La porte logique « OU»

|   | Table de vérité |   |

|---|-----------------|---|

| A | В               | S |

| 0 | 0               | 0 |

| 0 | 1               | 1 |

| 1 | 0               | 1 |

| 1 | 1               | 1 |

# Brève présentation du logiciel ISIS- PROTEUS

Le logiciel ISIS Proteus est un logiciel de réalisation des cartes électroniques qui permet aussi la simulation de montages électroniques.

5

Le Module ISIS qui permet de :

- 1. La saisie de schéma : La saisie d'un schéma structurel d'un circuit électronique (assemblage de composants électroniques dont on fixe les valeurs et les références) reliés par des connexions électrique (fils).

- 2. La simulation du comportement : Le lancement ISIS permet la simulation du comportement des composants du schéma. Ce simulateur effectue des calculs en se basant sur des modèles mathématiques.

# Démarche pour faire une simulation

- ✓ Ouvrir ISIS

- ✓ Ouvrir le gestionnaire de DEVICES (libraires de composants) en appuyant sur la touche

P

- ✓ Choisir les composants que l'on souhaite ajouter au schéma en tapant son nom dans la rubrique « Mots clés » Exemple taper « AND » pour la porte logique ET. Eventuellement sélectionner en dessous une catégorie de composants pour affiner la recherche [TTL 74LS series] et toujours pour affiner la recherche vous pouvez sélectionner une sous-catégorie.

- ✓ Une fois le composant trouvé, double cliquer avec le bouton gauche de la souris sur le composant désirer pour le faire apparaître dans la liste des composants du projet (à gauche de l'écran : DEVICES).

- ✓ Répéter l'opération autant de fois que nécessaire en re-saisissant un nouveau mot clé pour chercher un autre composant, le rajouter par double clic à la liste DEVICES.

- ✓ Placer les composants sur la feuille.

- ✓ Editer les propriétés des composants [Clic droit sur le composant -> Editer propriétés].

- ✓ Effectuer les connexions électriques entres les composants avec des liaisons électriques.

- ✓ Lancer la simulation (touche d'espace)

# ✓ Liste des composants utilisés dans ce TP

Pour ajouter des composants il va falloir aller les chercher dans les bibliothèques du logiciel (clic droit de la souris puis Component puis « **Pick Device** »).

| Nom réel du composant                       | Le nom sous Proteus | catégorie       | bib    |

|---------------------------------------------|---------------------|-----------------|--------|

| La porte logique ET à 2 entées              | 74LS08              | TTL 74LS series | TTL    |

| La porte logique NON-ET à 2 entées          | 74LS00              | TTL 74LS series | TTL    |

| La porte logique OU à 2 entées              | 74LS32              | TTL 74LS series | TTL    |

| La porte logique NON-OU à 2 entées          | 74LS02              | TTL 74LS series | TTL    |

| La porte logique OU-<br>EXCLUSIF à 2 entées | 74LS386             | TTL 74LS series | TTL    |

| La porte logique NON                        | 74LS04              | TTL 74LS series | TTL    |

| Générateur d'état logique                   | LOGICSTATE          | Debugging tools | Active |

| Sonde d'état logique                        | LOGICPROBE<br>(BIG) | Debugging tools | Active |

6

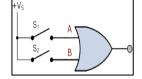

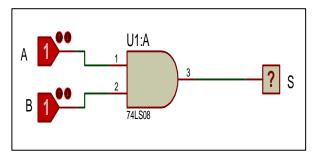

# ✓ Test des portes logiques de base

Réalisez dans Proteus le Montage 1 utilisant une porte logique ET **74LS08**, deux générateurs logiques **LOGICSTATE** en entrée et une sonde logique **LOGICPROBE** (**BIG**) en sortie.

Lancez la simulation, cliquez sur les générateurs **LOGICSTATE** puis vérifier la table de vérité du montage 1 de la sortie **S** en fonction des entrées **A** et **B**.

Figure 1. 3 La porte logique ET 74LS08

## Travail à faire

#### • La porte logique NON-ET

- 1. tracer le schema d'un circuit comprenant deux boutons-poussoirs, un opérateur NON-ET ou « NAND » et une LED.

- 2. Remplir la table de vérité suivante :

- 3. Déduire le fonctionnement de la porte NON-ET

| Table de verite  |   |   |

|------------------|---|---|

| $\boldsymbol{A}$ | В | S |

| 0                | 0 |   |

| 0                | 1 |   |

| 1                | 0 |   |

| 1                | 1 |   |

# • La porte logique OU

- 1. tracer le schema d'un circuit comprenant deux boutons-poussoirs, un opérateur OU ou « OR » et une LED.

- 2. Remplir la table de vérité suivante :

- 3. Déduire le fonctionnement de la porte OU

| Table de vérité  |   |   |

|------------------|---|---|

| $\boldsymbol{A}$ | В | S |

| 0                | 0 |   |

| 0                | 1 |   |

| 1                | 0 |   |

| 1                | 1 |   |

# • La porte logique NON-OU

1. tracer le schema d'un circuit comprenant deux boutons-poussoirs, un opérateur NON-OU ou « NOR » et une LED.

7

- 2. Remplir la table de vérité suivante :

- 3. Déduire le fonctionnement de la porte NON-OU

| Table de vérité  |   |   |

|------------------|---|---|

| $\boldsymbol{A}$ | В | S |

| 0                | 0 |   |

| 0                | 1 |   |

| 1                | 0 |   |

| 1                | 1 |   |

# • La porte logique XOR

1. tracer le schema d'un circuit comprenant deux boutons-poussoirs, un opérateur ou « XOR » et une LED.

| Table de vérité  |   |   |

|------------------|---|---|

| $\boldsymbol{A}$ | В | S |

| 0                | 0 |   |

| 0                | 1 |   |

| 1                | 0 |   |

| 1                | 1 |   |

- 2. Remplir la table de vérité suivante :

- 3. Déduire le fonctionnement de la porte XOR

- Application 1

Créez une table de vérité à trois colonnes pour les entrées A, B et C et une colonne pour la sortie. Elle doit illustrer l'équation suivante

$$S=(A+B).C$$

Réalisez ensuite le montage et vérifiez qu'il fonctionne correctement. Complétez la table ciaprès.

| Table de vérité  |   |   |   |

|------------------|---|---|---|

| $\boldsymbol{A}$ | В | C | S |

|                  |   |   |   |

|                  |   |   |   |

|                  |   |   |   |

|                  |   |   |   |

|                  |   |   |   |

|                  |   |   |   |

|                  |   |   |   |

|                  |   |   |   |

8

# TP N°2 : Etude et réalisation des fonctions logiques

#### **BUT DU TP:**

Les objectifs de ce TP sont :

- Maitriser les opérations d'Algèbre de Boole et ses propriétés.

- Apprendre le Théorème de DEMORGAN

- Apprendre à brancher un circuit intégré (CI) logique.

- > Apprendre à réaliser un montage électronique sur une plaque d'essai

- Apprendre à réaliser un logigramme réel en utilisant des portes logiques électroniques.

# RAPPEL THEORIQUE

- Le branchement d'un circuit intégré logique :

- Les fonctions logiques vues sont en réalité fabriquées dans des circuits intégrés

- La base des circuits logiques sont des transistors

- Un circuit intégré contient plusieurs portes logiques

- Pour repérer le brochage d'un circuit intégré, chacune de ces bornes porte un numéro

- $\bullet$  Un ergo sur le boîtier du circuit intégré permet de repérer la borne  $n^\circ 1$

- Il existe deux familles (TTL et CMOS) de circuits logiques.

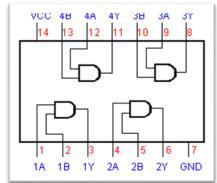

Figure 2. 1 le circuit intégré logique

| TTL                          | CMOS                         |

|------------------------------|------------------------------|

| Transistar Transistar Lagia  | Complementary Metal Oxide    |

| Transistor Transistor Logic  | Semiconductor                |

| BJT+ résistances + sup       | Transistor à effet de champs |

| Consomme plus d'énergie 10mW | Consomme moins d'énergie 1nW |

| TTL sont plus robuste        | Les CMOS sont plus sensible  |

| TTL commence par 74          | CMOS et sous la forme 4000   |

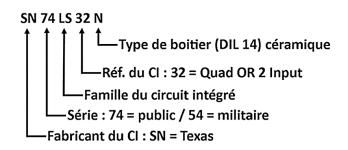

• La référence disponible sur le boîtier d'un circuit intégré nous informe sur sa famille et sur sa fonction logique (porte ET, porte OU-NON, etc.)

9

• Pour connaître le brochage exact d'un nouveau circuit intégré il faut consulter le **DATASHEET**.

Figure 2. 2 •Le branchement d'un circuit intégré

- Il est possible de connecter électriquement entre plusieurs portes logiques à l'aide d'un fil électrique reliant la sortie d'une porte à l'entrée d'une autre, et construire ainsi un logigramme

- Simplifier un logigramme en réduisant le nombre de portes logiques utilisées revient à simplifier son montage électronique, c'est-à-dire à utiliser moins de fils électriques, moins de circuits intégrés, et revient donc à réaliser une solution moins complexe, moins fragile, moins chère, avec moins de risques d'erreur et plus rapide à réaliser

- L'utilisation de l'algèbre de Boole participe donc à la simplification des montages électroniques.

# • Les propriétés des opérations de base

Quelques propriétés remarquables sont à connaitre :

| Fonction   | OU                          | ET                    | Commentaires         |

|------------|-----------------------------|-----------------------|----------------------|

|            | A+A=A                       | A.A=A                 | Idempotence          |

|            | A+I=I                       | A.0=0                 | Elément<br>absorbant |

| 1 variable | A+0=A                       | A.I=A                 | Elément<br>Neutre    |

|            | $A + \overline{A} = I$      | A. $\overline{A} = 0$ | Complément           |

|            | $\overline{\overline{A}} =$ | A                     | Involution           |

| Fonction OU |                       | ET                    | Commentaires   |  |  |

|-------------|-----------------------|-----------------------|----------------|--|--|

| 2 variables | A+B=B+A               | A.B=B.A               | Commutativité  |  |  |

| 2           | A+(B+C)=(A+B)+C=A+B+C | A.(B.C)=(A.B).C=A.B.C | Associativité  |  |  |

| 3 variables | A+(B.C)=(A+B).(A+C)   | A.(B+C)=A.B+A.C       | Distributivité |  |  |

10

# • Les théorèmes de l'algèbre de Boole

Pour effectuer tout calcul Booléen, on utilise, en plus des propriétés, un ensemble de théorèmes

| Théorème de | OU                                           | ET                                             |

|-------------|----------------------------------------------|------------------------------------------------|

| DEMORGAN    | $\overline{A+B} = \overline{A}.\overline{B}$ | $\overline{A.B} = \overline{A} + \overline{B}$ |

Branchage des circuits intégrés utilisés

# Partie expérimentale

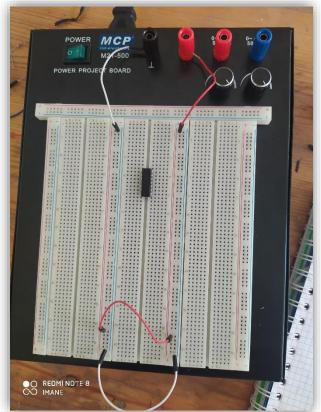

Pour tester les portes logiques, on va utiliser <u>une plaque d'essai.</u> La plaque d'essai, ou breadboard en anglais, est un outil fondamental dans le prototypage électronique et la

conception de circuits. Voici une explication de ses composants et de leur utilisation typique :

Bandes de bornes : La plaque d'essai comprend deux bandes verticales sur ses côtés appelées bandes de bornes. Ces bandes s'étendent généralement sur toute la longueur de la platine. Chaque trou ou douille dans la bande de bornes est connecté électriquement verticalement, ce qui signifie que tous les trous dans une colonne particulière sont connectés ensemble. Ces bandes sont souvent utilisées pour connecter des composants résistances. que des des d'autres condensateurs et éléments discrets.

Bandes de bus : La plaque d'essai comporte également deux bandes horizontales le long des bords supérieur et inférieur. Ces bandes sont principalement utilisées pour les connexions d'alimentation,

Figure 2. 3 La plaque d'essai

La conception de la plaque d'essai permet de réaliser facilement et temporairement des connexions entre les composants sans avoir besoin de souder. Des composants tels que des circuits intégrés (CI), des capteurs et des fils de connexion peuvent être insérés dans les trous de la platine d'essai pour créer un circuit.

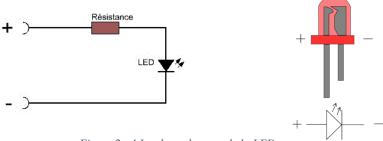

Allumer une LED

11

## Travail à faire

# • Application 1

✓ Sur une plaque d'essai, réaliser le montage suivant :

Figure 2. 4 Lae bronchement de la LED

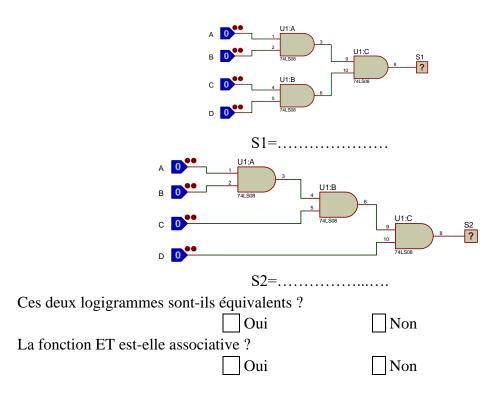

#### • Application 2 : Associativité de la porte logique ET

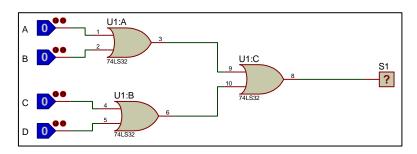

Voici 2 logigrammes différents à 4 entrées (A, B, C et D). La sortie du premier logigramme s'appelle S1 et la sortie du second s'appelle S2. Sachant que <u>deux logigrammes sont équivalents</u> seulement si leurs tables de vérité sont strictement identiques,

- 1. Donner les références des circuits intégrés logiques utilisé pour réaliser ces logigrammes

- 2. Indiquez le n° des pattes des circuits intégrés sur les entrées et sur les sorties des portes logiques sur le logigramme

- 3. Câblez votre solution sur la plaque d'essai, testez-la en essayant chacune des 4 lignes de la table de vérité.

- 4. Corrigez votre montage en cas de disfonctionnement, puis faites valider votre montage final au professeur une fois qu'il fonctionne correctement.

- 5. complétez ci-contre la table de vérité de S1 et de S2

12

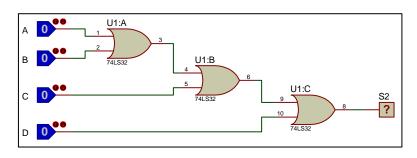

# Application 3 : Associativité de la porte logique OU :

On étudie maintenant les deux logigrammes suivants.

- 1. Donner les références des circuits intégrés logiques utilisé pour réaliser ce logigramme

- 2. Indiquez le n° des pattes des circuits intégrés sur les entrées et sur les sorties des portes logiques sur le logigramme

- 3. Câblez votre solution sur la plaque d'essai, testez-la en essayant chacune des 4 lignes de la table de vérité.

- 4. Corrigez votre montage en cas de disfonctionnement, puis faites valider votre montage final au professeur une fois qu'il fonctionne correctement.

Sans remplir de table de vérité mais en utilisant seulement vos observations précédentes répondez aux questions ci-dessous :

Ces deux logigrammes sont-ils équivalents?

Oui Non

La fonction OU est-elle associative?

Oui Non

# • Application 4 : Allumage conditionnel de deux LEDs

Deux interrupteurs A, B commandent l'allumage de 2 LEDs S et R suivant les conditions suivantes :

13

- ✓ La LED S ne doit s'allumer que si les 2 interrupteurs sont activés.

- ✓ Dès qu'un ou plusieurs interrupteurs sont activés la LED R doit s'allumer,

On associe aux deux interrupteurs a, b deux variable logiques A, B, telles que : si un interrupteur est activé, la variable logique lui correspondant est à l'état 1.

#### • La LED S

- 5. Donner la table de vérité liant A, B à S

- 6. Calculer l'expressions de la fonction logique S et dessiner leur logigramme

| $\boldsymbol{A}$ | В | S |

|------------------|---|---|

| 0                | 0 |   |

| 0                | 1 |   |

| 1                | 0 |   |

| 1                | 1 |   |

S=.....

- 7. Donner les références des circuits intégrés logiques utilisé pour réaliser ce logigramme

- 8. Indiquez le n° des pattes des circuits intégrés sur les entrées et sur les sorties des portes logiques sur le logigramme

- 9. Câblez votre solution sur la plaque d'essai, testez-la en essayant chacune des 4 lignes de la table de vérité.

- 10. Corrigez votre montage en cas de disfonctionnement, puis faites valider votre montage final au professeur une fois qu'il fonctionne correctement.

- 11. Simplifier l'expression de S et dessiner leur logigramme à l'aide de portes NON-OU.

- 12. Indiquez le n° des pattes des circuits intégrés sur les entrées et sur les sorties des portes logiques sur le logigramme

- 13. Câblez votre solution sur la plaque d'essai, testez-la en essayant chacune des 4 lignes de la table de vérité.

Corrigez votre montage en cas de disfonctionnement, puis faites valider votre montage final au professeur une fois qu'il fonctionne correctement.

#### La LED R

- 1. Donner la table de vérité liant A, B à R

- 2. Calculer l'expressions de la fonction logique R et dessiner leur logigramme

| 0     | 0 |  |

|-------|---|--|

| 0     | 1 |  |

| <br>1 | 0 |  |

| 1     | 1 |  |

R

$\boldsymbol{A}$

| R= | <br> |  |  |  |  |  |  |  |  |  |  |  |  |  |

|----|------|--|--|--|--|--|--|--|--|--|--|--|--|--|

|    |      |  |  |  |  |  |  |  |  |  |  |  |  |  |

- 3. Donner les références des circuits intégrés logiques utilisé pour réaliser ce logigramme

- 4. Indiquez le n° des pattes des circuits intégrés sur les entrées et sur les sorties des portes logiques sur le logigramme

14

- 5. Câblez votre solution sur la plaque d'essai, testez-la en essayant chacune des 4 lignes de la table de vérité.

- 6. Corrigez votre montage en cas de disfonctionnement, puis faites valider votre montage final au professeur une fois qu'il fonctionne correctement.

| 7. | Simplifier l'expression de R et dessiner leur logigramme à l'aide de portes NON-ET.  R=                                                             |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 8. | Indiquez le n° des pattes des circuits intégrés sur les entrées et sur les sorties des portes logiques sur le logigramme                            |

| 9. | Câblez votre solution sur la plaque d'essai, testez-la en essayant chacune des 4 lignes de la table de vérité.                                      |

| 10 | . Corrigez votre montage en cas de disfonctionnement, puis faites valider votre montage final au professeur une fois qu'il fonctionne correctement. |

| Q  | uestions                                                                                                                                            |

| 1. | Les deux logigrammes pour chaque allumage des LEDs sont-ils équivalents ?                                                                           |

|    | Oui Non                                                                                                                                             |

| 2  | Comment on peut identifier un circuit intégré ?                                                                                                     |

3. Comment sont représentées les 0 logiques et les 1 logiques dans un montage

15

électronique.

# TP N°3: Etude et réalisation d'un Multiplexeur par des Portes Logiques

#### **BUT DU TP:**

Les objectifs de ce TP sont :

- Apprendre à brancher un circuit intégré (CI) logique.

- Familiariser avec les Multiplexeurs

- Familiariser avec les Démultiplexeurs

- Analyse Des Multiplexeurs Intégrés le 74157, le 74153.

- Analyse Des Démultiplexeurs Intégrés le 74157, le 74153.

# RAPPEL THEORIQUE

#### • MULTIPLEXEUR

C'est un circuit combinatoire logique qui comporte 2<sup>N</sup> entrées, et N entrées de sélection et une seule sortie.

Le multiplexeur circuit d'aiguillage qui permet la sélection d'une entrée vers la sortie suivant le sélecteur.

Un exemple courant d'utilisation des multiplexeurs est dans les systèmes de communication, où plusieurs signaux provenant de différentes sources doivent être transmis à travers un seul canal de communication. Les multiplexeurs sont utili sés pour sélectionner et combiner ces signaux en un seul flux de données à transmettre.

Un autre exemple est dans les systèmes informatiques, où les Figure 3. 1 Multiplexeur

multiplexeurs peuvent être utilisés pour sélectionner une source de données parmi plusieurs périphériques d'entrée (comme des claviers, des souris ou des capteurs) et les transmettre au processeur ou à la mémoire centrale du système.

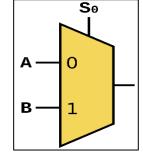

# • Etude d'un multiplexeur 2 => 1

C'est multiplexeur qui possède deux entrées A et B, une entrée de sélection S

#### La table de vérité

| S | A | В | Y |

|---|---|---|---|

| 0 | 0 | X | 0 |

| 0 | 1 | X | 1 |

| 1 | X | 0 | 0 |

| 1 | X | 1 | 1 |

#### <u>L'équation logique du multiplexeur 2 à 1</u>

D'après la table de vérité, on peut déduire que :

$$S=0$$

$\rightarrow$   $Y=A$

$S=1$   $\rightarrow$   $Y=B$

Alors,

$$Y = A\overline{S} + BS$$

## Démultiplexeur

Définition : Un démultiplexeur est un circuit logique combinatoire à plusieurs entrées et plusieurs sorties, conçu pour acheminer sélectivement des données provenant d'une seule entrée de données vers une sortie spécifique en fonction des signaux de commande appliqués à ses entrées de commande.

**Applications**: Les démultiplexeurs sont largement utilisés dans les systèmes de transmission de données et de communication pour diviser un flux de données en plusieurs canaux distincts. Ils sont également utilisés dans la conception de circuits électroniques complexes, tels que les mémoires, les systèmes de commande et les circuits de traitement de signal.

Figure 3. 2 Démultiplexeur

# • Le démultiplexeur a deux voies

Le schéma symbolique et l'équivalent mécanique d'un démultiplexeur à 2 voies sont présentés

Figure 3. 3 Démultiplexeur 1 à 2

En général pour A = 0, la sortie S0 est sélectionnée et pour A = 1 c'est la sortie S1; la sortie non sélectionnée étant à l'état 1.

Le circuit combinatoire qui réalise la fonction du démultiplexeur à 2 voies doit donc correspondre à la table de vérité

#### Les équations logiques du démultiplexeur 1 à 2

De cette table, on déduit immédiatement que

$$S0 = A + D$$

.

Et l'équation de S1 suivante :

$$S1 = \overline{A} + D$$

| Ent | rées | Soi | rtis |  |  |

|-----|------|-----|------|--|--|

| D   | A    | S0  | S1   |  |  |

| 0   | 0    | 0   | 1    |  |  |

| 1   | 0    | 1   | 1    |  |  |

| 0   | 1    | 1   | 0    |  |  |

| 1   | 1    | 1   | 1    |  |  |

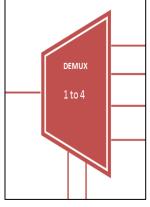

# • Etude un démultiplexeur 1 =>4

La donnée présente en E1 est aiguillée vers  $D_0$ ,  $D_1$ ,  $D_2$  ou  $D_3$  selon l'état des entrées de commande A et B.

| В | A | $\mathbf{D}_0$ | $\mathbf{D}_1$ | $\mathbf{D}_2$ | <b>D</b> <sub>3</sub> |

|---|---|----------------|----------------|----------------|-----------------------|

| 0 | 0 | E1             | 0              | 0              | 0                     |

| 0 | 1 | 0              | E1             | 0              | 0                     |

| 1 | 0 | 0              | 0              | E1             | 0                     |

| 1 | 1 | 0              | 0              | 0              | E1                    |

Figure 3. 4 Démultiplexeur 1 à 4

## Les équations logiques du démultiplexeur 1 à 4

Les équations de sortis sont :

$$D_0 = E_1 \bar{A} \bar{B}$$

$$D_1 = E_1 A \bar{B}$$

$$D_2 = E_1 \bar{A} B$$

$$D_3 = E_1 A B$$

Remarque: On remarquera qu'un démultiplexeur est semblable à un décodeur (sélecteur d'une sortie parmi plusieurs), la seule différence avec le décodeur étant l'entrée des données E. Les décodeurs intégrés possèdent le plus souvent une entrée de validation, celle-ci peut alors servir d'entrée de données ce qui permet alors de transformer le décodeur en démultiplexeur. C'est une des raisons qui fait que les fabricants de circuits intégrés donnent

18

# Branchage des circuits intégrés utilisés

• Pour fonctionner, un circuit intégré logique doit être alimenté entre 0 V et 5 V par ces bornes 8 et 16

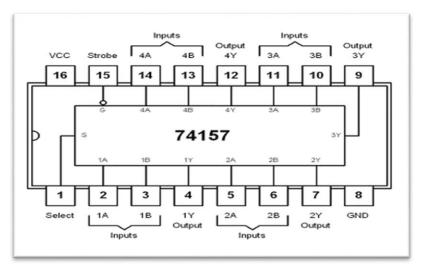

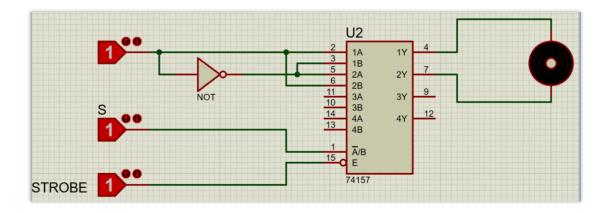

# MULTIPLEXEUR INTÉGRÉ À 2 VOIES : LE 74157

Figure 3. 5 Multiplexeur 74157

Le brochage et le schéma logique de ce circuit intégré et sa table de vérité sont donnés par les figures précédentes (*datasheet*).

|        | Inputs |   |   |          |  |  |  |  |  |  |

|--------|--------|---|---|----------|--|--|--|--|--|--|

| Strobe | Select | A | В | Output Y |  |  |  |  |  |  |

| Н      | X      | X | X | L        |  |  |  |  |  |  |

| L      | L      | L | X | L        |  |  |  |  |  |  |

| L      | L      | Н | X | Н        |  |  |  |  |  |  |

| L      | Н      | X | L | L        |  |  |  |  |  |  |

| L      | Н      | X | Н | Н        |  |  |  |  |  |  |

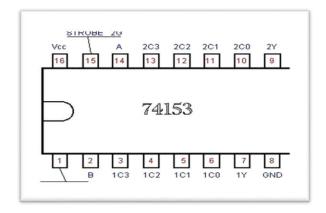

# • MULTIPLEXEUR INTÉGRÉ À 4 VOIES : LE 74153

Le circuit intégré 74153 contient deux multiplexeurs à 4 voies à entrées de sélection A et B communes. Chaque multiplexeur dispose d'une entrée de validation E (STROBE). Celle-ci, portée à l'état 1, force la sortie du multiplexeur correspondant à l'état 0 indépendamment de l'état des autres entrées.

19

| Inp | Output |    |

|-----|--------|----|

| В   | A      | Y  |

| 0   | 0      | C0 |

| 0   | 1      | C1 |

| 1   | 0      | C2 |

| 1   | 1      | C3 |

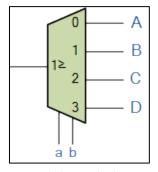

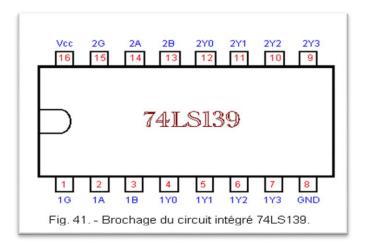

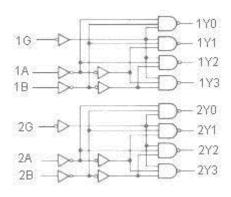

• Démultiplexeur intégré à 4 voies : le 74LS139

Le circuit intégré **74LS139** contient deux démultiplexeurs à **4 voies**. Chacun d'eux possède 2 entrées de sélection **A** et **B**, une entrée de données **G** et **4 sorties** (**Y0** à **Y3**).

Figure 3. 6 Multiplexeur 74153

Figure 3. 7 Démultiplexeurs 74LS139

Le brochage et le schéma logique de ce circuit sont donnés à la figure suivante donne sa table de vérité.

Figure 3. 8 Le brochage de démultiplexeurs 74LS139

|   | Entrées |   |    | Soi | rtis |    |

|---|---------|---|----|-----|------|----|

| G | В       | A | Y0 | Y1  | Y2   | Y3 |

| 1 | X       | X | 1  | 1   | 1    | 1  |

| 0 | 0       | 0 | 0  | 1   | 1    | 1  |

| 0 | 0       | 1 | 1  | 0   | 1    | 1  |

| 0 | 1       | 0 | 1  | 1   | 0    | 1  |

| 0 | 1       | 1 | 1  | 1   | 1    | 0  |

# Le montage d'un multiplexeur 2 à 1

- 1. Donner un logigramme d'un multiplexeur 2 à 1 en utilisant seulement les portes logiques NON-ET

- ✓ Réalisez dans Proteus le montage utilisant un circuit intégré 74LS00

- ✓ Lancez la simulation du Montage puis vérifier la table de vérité d'un MUX 2 à 1

- Analyse d'un multiplexeur intégré à 2 voies : Le 74157

Remplacer le montage précèdent d'un MUX 2 à 1 en utilisant seulement CI 74157 dans Proteus.

# Le montage d'un multiplexeur 4 à 1

- Analyse d'un multiplexeur intégré à 4 voies : le 74153

- ✓ Dans le Proteus, réaliser un MUX 4 à 1 en utilisant un circuit intégré 74153

- ✓ Vérifier la table de vérité

- APPLICATION1: Commander le sens de rotation d'un moteur DC

- ✓ Sur Proteus, réaliser le montage suivant :

- ✓ Varie les valeurs des entrées du multiplexeur et déduire le fonctionnement du montage

- APPLLICATION 2 : Le contrôle d'une cale d'un navire

Un navire, destiné au transport d'éléments liquides, comporte dans sa cale trois réservoirs A, B, C.

Le voyant S s'allume quand "l'assiette est correcte", c'est à dire quand les charges sont bien

#### réparties.

Le voyant S s'allume pour les cas suivants :

- Réservoirs A et C vides, réservoir B rempli.

- Réservoirs A et C remplis, réservoir B vide.

- Les trois Réservoir sont remplies.

- Les trois réservoirs sont vides.

#### Travail demandé

- 1. Donner la table de vérité correspond au fonctionnement du voyant S.

- 2. Simplifier la fonction logique de la sortie (l'algèbre de Boole et la table de Karnaugh)

- 3. Simuler le fonctionnement de la fonction S.

- 4. Simuler le fonctionnement de S en utilisant seulement les portes logiques NAND

- 5. Simuler le fonctionnement de la fonction S en utilisant un multiplexeur 8 à 1.

# Le montage d'un multiplexeur 1 à 4

- 2. Donner un logigramme d'un multiplexeur 1 à 4 en utilisant seulement les portes logiques NON-ET

- ✓ Réalisez dans Proteus le montage utilisant un circuit intégré 74LS00

- ✓ Lancez la simulation du Montage puis vérifier la table de vérité d'un MUX 2 à 1

- Analyse d'un démultiplexeur intégré à 4 voies : LE 74LS139

Remplacer le montage précèdent d'un DEMUX 1 à 4 en utilisant seulement CI 74LS139 dans Proteus.

22

## **Questions**

- ✓ Quel est le rôle d'un multiplexeur ?

- ✓ Quel est le rôle d'un démultiplexeur ?

- ✓ Quelle est la fonction de l'entrée S?

- ✓ Quelle est la fonction de STROBE E ?

# TP N° 4 : Etude et réalisation d'un circuit combinatoire arithmétique

## **BUT DU TP:**

Les objectifs de ce TP sont :

- Réalisation d'un circuit additionneur de 2 nombres à 4 bits.

- Le demi-additionneur

- L'additionneur complet

- Réalisation d'un circuit soustracteur de 2 nombres à 4 bits.

- Le demi-soustracteur

- Le soustracteur complet

- Branchage d'un circuit intégré 74LS83

# RAPPEL THEORIQUE

#### L'additionneur

Un additionneur est un circuit logique permettant de réaliser une addition. Ce circuit est très présent dans les ordinateurs pour le calcul arithmétique mais également pour le calcul d'adresses, d'indice de tableau dans le processeur. On dénombre deux types d'additionneurs : Le demi-additionneur et l'additionneur complet.

#### Le demi-additionneur de 2 nombres à 4 bits

Au niveau du poids le plus bas, il n'y a pas de retenue provenant du rang inférieur. On peut donc se contenter d'un système simple réalisant uniquement la somme des deux bits a et b. Un tel système est appelé demi-additionneur.

#### Travail demandé

- a) Ecrire la table de vérité de ce système ayant pour variables d'entrées a et b et comme fonctions de sortie  $\Sigma_i$  et  $C_i$ .

- b) Réaliser le circuit et vérifier son fonctionnement. On utilisera des AND (7408), des OR (7432) et des NOT (7404).

23

# L'additionneur complet de 2 nombres à 4 bits

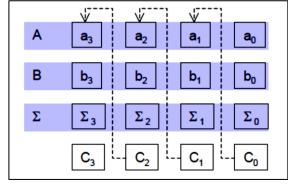

On considère deux nombres A et B que nous supposerons fixés à 4 éléments binaires. La somme de A et B est obtenue de la manière présentée à la Figure 1.

Le somme de  $a_0$  et  $b_0$  donne un résultat partiel  $\Sigma_0$ et une retenue  $C_0$  qui est utilisée avec les chiffres suivants. On forme alors la somme de  $a_1$ ,  $b_1$ , et  $C_0$ pour obtenir une somme partielle  $\Sigma_1$  et une Figure 4. 1 Principe de l'addition sur 4 bits.

retenue C<sub>1</sub> et ainsi de suite. La dernière retenue C<sub>3</sub> n'est pas utilisée car il n'y a plus d'éléments binaires suivants dans A et B.

Le circuit réalisant la somme de A et B comprend donc 4 sous-ensembles identiques ayant chacun 3 entrées  $a_i$ ,  $b_i$  et  $C_{i-1}$  et 2 sorties  $\Sigma_i$  et  $C_i$  comme le montre la Figure 2 suivante.

Figure 4. 2 Architecture de l'additionneur.

Tous les étages autres que l'étage correspondant au poids le plus faible impliquent la prise en compte de la retenue venant du rang immédiatement inférieur. Les systèmes de ce type sont appelés *additionneurs complets*. Ils ont 3 variables d'entrées  $a_i$ ,  $b_i$  et  $C_{i-1}$  et deux fonctions de

sorties

$$\Sigma_i$$

et  $C_i$ .

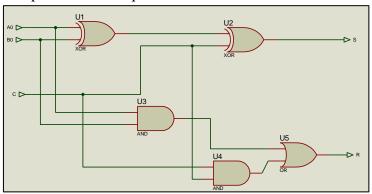

#### • Travail demandé

- a) Ecrire la table de vérité d'un tel additionneur. En déduire les expressions logiques de  $\Sigma_i$  et  $C_i$ .

- b) Construire un additionneur complet à partir de 2 *demi-additionneurs*. Pour cela, on utilisera des XOR et des NAND.

# Additionneur en circuit intégré

Le circuit 7483 est un additionneur 4 bits. Il réalise la somme des nombres A  $(a_3 a_2 a_1 a_0)$  et B  $(b_3 b_2 b_1 b_0)$ .

#### • Travail demandé

- a) Vérifier le fonctionnement de ce circuit en utilisant sa documentation fournie en annexe.

- b) Réaliser un additionneur à 6 bits en utilisant deux circuits 74LS83. Donner alors le schéma et les explications correspondantes.

#### Le soustracteur

Le problème est analogue à celui rencontré dans le cas de l'additionneur. On se propose de réaliser une soustraction (A-B) entre deux nombres positifs. On est amené tout naturellement, comme cela avait été fait lors de l'étude de l'additionneur, à construire un *demi-soustracteur*, puis un *soustracteur complet*.

#### • Le demi-soustracteur

La soustraction entre a et b se fait avec un circuit combinatoire logique qui a deux entrées uniquement et deux sorties : D la différence et C l'emprunt.

On désire construire un système effectuant la différence  $D_i$  entre 2 bits  $a_i$  et  $b_i$ . On appellera  $C_i$  l'emprunt.

#### • Travail demandé

- a) Ecrire la table de vérité du demi-soustracteur.

- b) En déduire les fonctions logiques D<sub>i</sub> et C<sub>i</sub>.

- c) Réaliser le circuit en utilisant des XOR (7486), des AND (7408), et des NOT (7404).

#### Le soustracteur complet

Il s'agit maintenant de passer au rang suivant, soustraire B de A mais avec une information supplémentaire qui est E0. Le circuit combinatoire possède toujours 2 sorties la différence D1 et l'emprunt E1, mais trois entrées A1, B1 et E0 : c'est le soustracteur du 2 ieme rang. Il est complet car par rapport au demi-soustracteur, celui-ci tient compte de l'emprunt fait à l'étage (rang) précédent.

#### • Travail demandé

- a) Ecrire la table de vérité.

- b) Montrer la manière de réaliser un soustracteur complet en utilisant 2 demi-soustracteurs.

- c) Réaliser un soustracteur à 2 bits à l'aide d'un demi-soustracteur et d'un soustracteur complet.

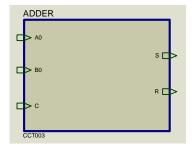

#### Créer des sous-circuits

Un sous-circuit (subcircuit mode) permet d'encapsuler tout un montage électronique dans un simple rectangle possédant des entrées et des sorties. Pour créer un sous-circuit, cliquez sur le bouton «subcircuit mode» puis tracez le rectangle symbolisant le sous-circuit. Pour ajouter des entrées au sous-circuit, cliquez sur INPUT dans le mode sous-circuit, puis cliquez sur le bord gauche du rectangle du sous-circuit. Pour ajouter des sorties au sous-circuit, cliquez sur OUTPUT dans le mode sous-circuit, puis cliquez sur le bord droit du rectangle du sous-circuit. Donnez un nom à chaque entrée et à chaque sortie en double-cliquant dessus. Pour éditer l'intérieur du sous circuit, cliquez droit sur le sous-circuit puis sur « GOTO CHILD SHEET » : vous pouvez alors saisir le schéma électronique interne du sous-circuit.

Figure 4. 3 Le sous-circuit.

Pour ajouter des entrées et utiliser INPUT et OUTPUT sorties les mêmes noms que

des sorties à votre schéma interne sur la feuille enfant, du « Mode terminal ». Donnez à vos entrées et à vos ceux utilisés sur le symbole du sous-circuit (en double-

cliquant dessus). Pour sortir de la feuille enfant du sous-circuit il faut cliquer sur « Revenir à la feuille parent » « **exit to Parent sheet** » dans le menu Projet. Enfin, il est parfaitement possible de créer un sous-circuit dans un sous-circuit, et structurer ainsi une carte électronique complexe en plusieurs niveaux répartis hiérarchiquement.

Figure 4. 4 La feuille enfant

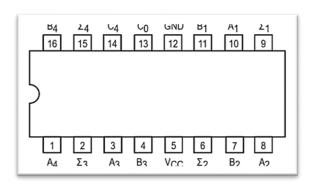

# Branchage des circuits intégrés utilisés

#### L'ADDITIONNEUR COMPLET A 4 BIT : LE 74LS83

Figure 4. 5 Additionneur 74LS83

Le 74LS83 est un additionneur complet binaire 4 bits à grande vitesse avec une anticipation de report interne. Il accepte deux mots binaires de 4 bits (A1–A4, B1–B4) et une entrée de retenue (C0). Il génère les sorties binaires Sum (R1–R4) et la sortie Carry (C4) à partir du bit le plus significatif

# TP N° 5 : Etude et réalisation d'un circuit séquentiel

## **BUT DU TP:**

Les objectifs de ce TP sont :

- Familiariser avec la logique séquentielle.

- Concevoir des différentes bascules RS, JKH ...

- Créer des compteurs asynchrones à partir des bascules.

# Logique séquentielle :

Un circuit séquentiel si l'état de ses sorties dépend des entrées mais également des états antérieurs des entrées ou sorties. Ces circuits

permettent entre autres :

- ✓ La mémorisation

- ✓ Le décalage

- ✓ Le comptage

Ils reposent sur les composants principaux Les bascules

Figure 5. 1 Circuit séquentiel

#### Les bascules

# • Les bascules asynchrones

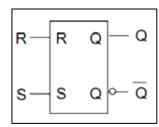

#### La bascule RS (Reset - Set):

Les noms R et S donnés aux entrées d'une bascule RS vienne de l'anglais :

- $\_$  R signifie « Reset » en anglais, ce qui veut dire « Mise à 0 » en français

- $\_$  S signifie « Set » en anglais, ce qui veut dire « Mise à 1 » en français

✓ La sortie change d'état de manière asynchrone dès que les entrées S ou R sont actives.

- ✓ Lorsque les entrées sont à 0, la sortie mémorise son état précédent.

- $\checkmark$  La configuration R = S = 1 a des effets dépendant de l'implantation électronique.

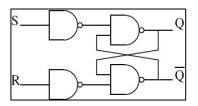

Une bascule RS peut être réalisée à l'aide de deux portes NOR (Non OU) ou de deux portes NAND et d'inverseurs

27

1. Dans le cas d'une bascule RS NOR:

$$Q = \overline{R + \overline{(S + Q)}} = \overline{R}(S + Q) \Rightarrow$$

**Reset** prioritaire si  $R = S = 1$

Figure 5. 2 Bascule RS.

Figure 5. 3 Bascule RS NOR

2. Dans le cas d'une bascule RS NAND :

$$Q = \overline{S.(\overline{R}.Q)} = S + (\overline{R}.Q) \Rightarrow$$

**Set** prioritaire si  $R = S = I$

- 1. Réalisez maintenant dans Proteus les deux Montages utilisant les portes logiques NAND, NOR.

- 2. Complétez la table de fonctionnement de la bascule RS à Figure 5. 4 Bascule RS NAND portes OU-NON récapitulant le fonctionnement que vous venez de constater

La table de fonctionnement de la bascule RS à portes NON-OU

| Entrées |   | sorties |   | Fonction réalisée |  |

|---------|---|---------|---|-------------------|--|

| R       | S | Q       | Q | Fonction reansee  |  |

| 0       | 0 |         |   |                   |  |

| 0       | 1 |         |   |                   |  |

| 1       | 0 |         |   |                   |  |

| 1       | 1 |         |   |                   |  |

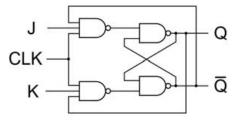

# • Les bascules synchrones

Sont des bascules asynchrones avec une troisième entrée pour le temps (t) (Horloge **H**) avec une période T, le changement de l'état de la sortie dépend de l'horloge H et l'état des entrées

#### La bascule JK:

Bascule **JK** est une bascule **RS** mais dans le cas où la valeur de deux entrées est 1 la sortie est porté la négation de l'état précédente.

Figure 5. 5 Bascule JK.

| K | J | $Q_{t+1}$   |

|---|---|-------------|

| 0 | 0 | Qt          |

| 1 | 0 | 0           |

| 0 | 1 | 1           |

| 1 | 1 | $\bar{Q}_t$ |

28

- 3. Réalisez maintenant dans Proteus

- 4.

# Les compteurs

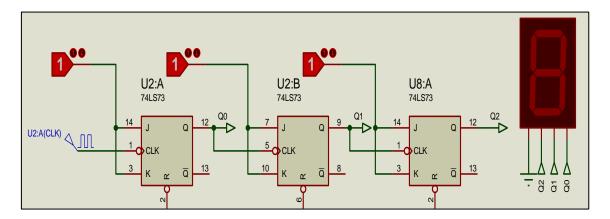

Les compteurs sont des ensembles des bascules montées en série ou en parallèle pour compter soit incrémenter ou décrémenté, on distingue deux types : les compteurs Asynchrone et Synchrone.

# • Les compteurs asynchrones à base de bascules JK

Sont formé par des bascules montées en série tel que chaque bascule donne l'impulsion à la bascule suivante

Un compteur modulo **n** peut compter de zéro jusqu'à (**n-1**), tel que : Si n=8 donc est compté de 0 à 7,

Soit le schéma ci-dessous :

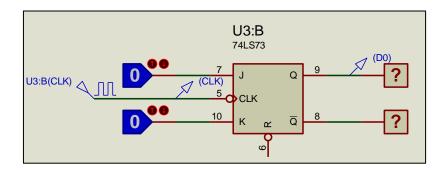

- 5. Saisir sous Isis (Proteus), le schéma du compteur ci-dessus (3 bascules JK référence 74LS73)

- 6. Indiquer le modulo du compteur, la valeur minimale et maximale du cycle.

- 7. Modifiez votre montage dans Proteus afin que le compteur compte jusqu'à 3

29

8. Créer un compteur modulo 16

# **Bibliographie**

- [1] Mano, M. Morris. (1979). Digital Logic and Computer Design. Pearson.

- [2] Floyd, Thomas L. (2014). Digital Fundamentals (11th ed.). Pearson.

- [3] **Kang, Sung-Mo, & Leblebici, Yusuf.** (2014). *CMOS Digital Integrated Circuits : Analysis and Design* (4th ed.). McGraw-Hill Education.

- [4] Wakerly, John F. (2017). Digital Logic Design (5th ed.). Pearson.

Dr. *I. GHLIB*

30