People's Democratic Republic of Algeria

Ibn Khaldoun University of Tiaret

Faculty of Applied Sciences

Electrical Engineering Department

## *Elements of Physics of Electronic Components*

Author: Dr. Youcef BELHADJI

Email: [youcef.belhadj@univ-tiaret.dz](mailto:youcef.belhadj@univ-tiaret.dz)

### Reviewed by

Pr. Djillali Nasri

Dr. Fateh Moulahcene

Ibn khaldoun University of Tiaret

Institute of Science and Applied Technology (SAT Institute), University of

Oum El Bouaghi

Academic Year: 2025–2026

## Course produced using numerous bibliographic references in an educational framework

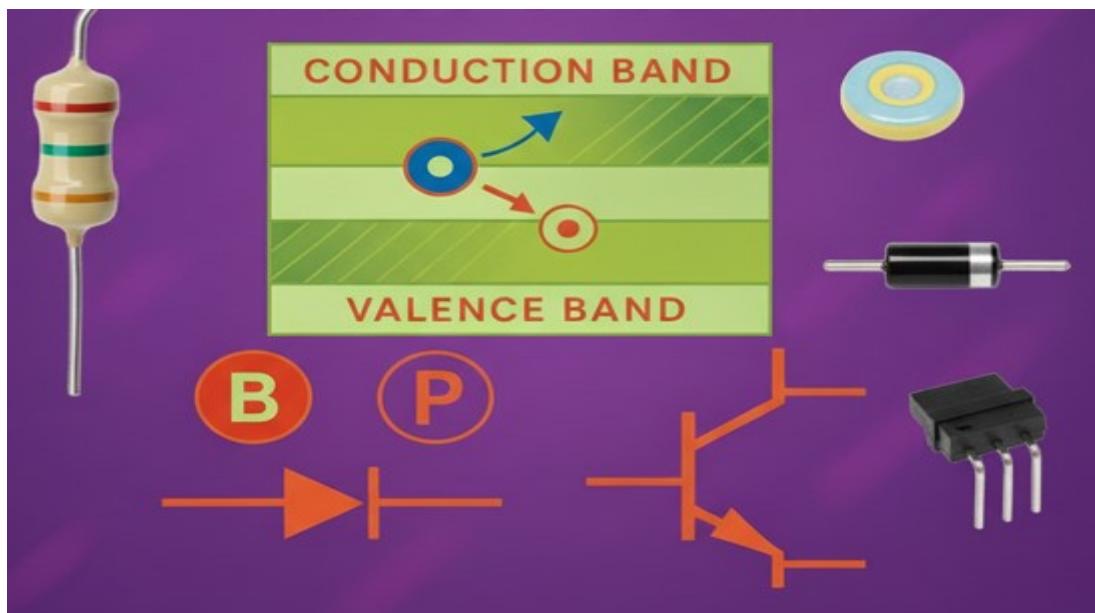

This comprehensive course covers the physics of semiconductor devices, from theoretical foundations (atomic and crystalline structure) to practical applications (diode, transistor, amplifiers and switches). It is structured progressively, allowing for an in-depth understanding of the essential concepts in microelectronics.

**Target audience:** Bachelor's and Master's students in electronics, semiconductor physics, and microelectronics.

### Table of content

| Chapter | Title                                 | Pages  | Main Content                                                  |

|---------|---------------------------------------|--------|---------------------------------------------------------------|

| I       | <b>Generalities on semiconductors</b> | 3–25   | Atomic bonds, crystal structure, defects, energy bands        |

| II      | <b>Electronic transport</b>           | 26–42  | Carrier statistics, Fermi level, electronic transport         |

| III     | <b>PN junction physics</b>            | 43–55  | Junction at equilibrium, biasing, I–V characteristics         |

| IV      | <b>Bipolar transistor (BJT)</b>       | 56–73  | Structure, biasing, operating modes, characteristics          |

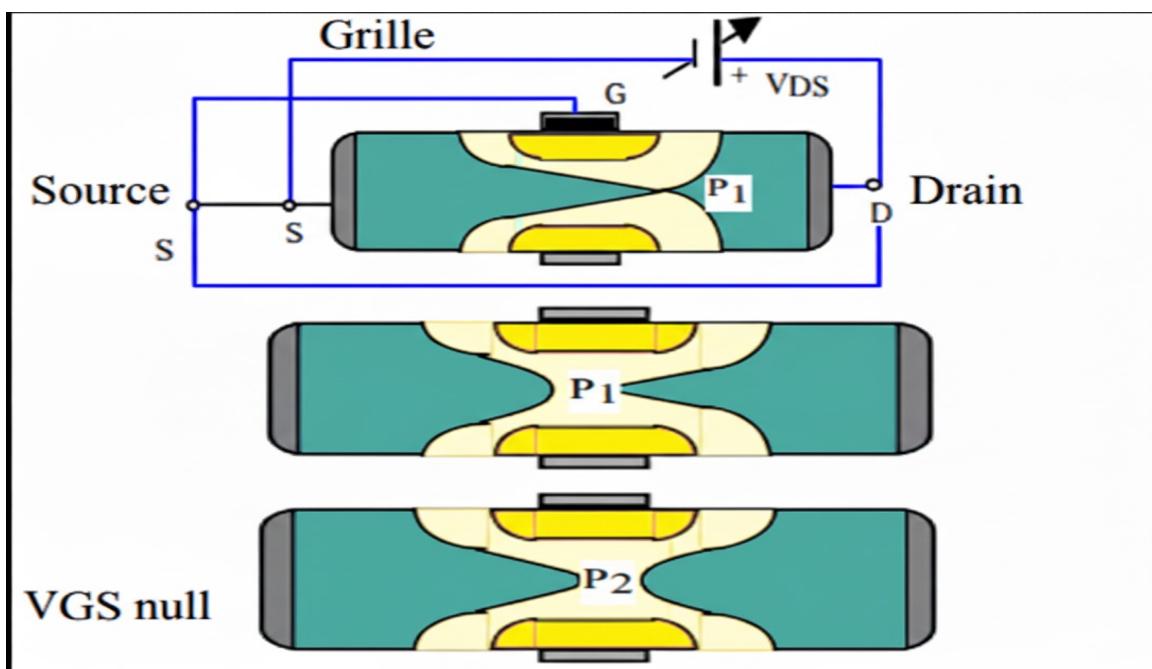

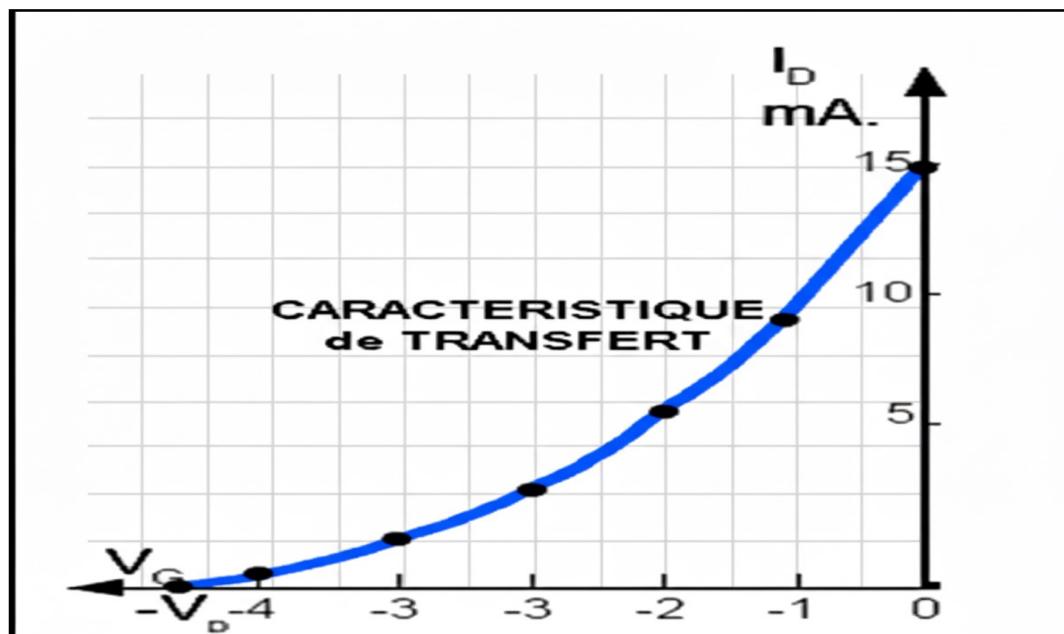

| V       | <b>Field effect transistor: JFET</b>  | 74–103 | Structure, characteristics, biasing, amplifier configurations |

**Total numbers of pages:** 104

**Academic year:** 2025-2026

## Chapter I: Generalities on semiconductors

### Introduction

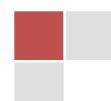

At the beginning of our education, in order to understand the phenomena and the nature of matter around us, we asked ourselves many questions such as: what does matter represent? How many states of matter are there? The answer to these questions was three states common to our experience. These states are: solid, liquid and gas. All these states are visible and occur regularly on earth. For example, rocks, ice and trees represent the solid state, water and many oils are liquids, while the atmosphere that surrounds us and we breathe is the gaseous state. However, in addition to these three common states, which are all based on the way atoms are arranged, we can cite another state namely the Plasma state. If an atom is bombarded with sufficient energy, electrons will be torn off and expelled, thus creating an ionized plasma, therefore the fourth state of matter (see figure 1.1).

**Figure 1.1:** The fundamental states of matter

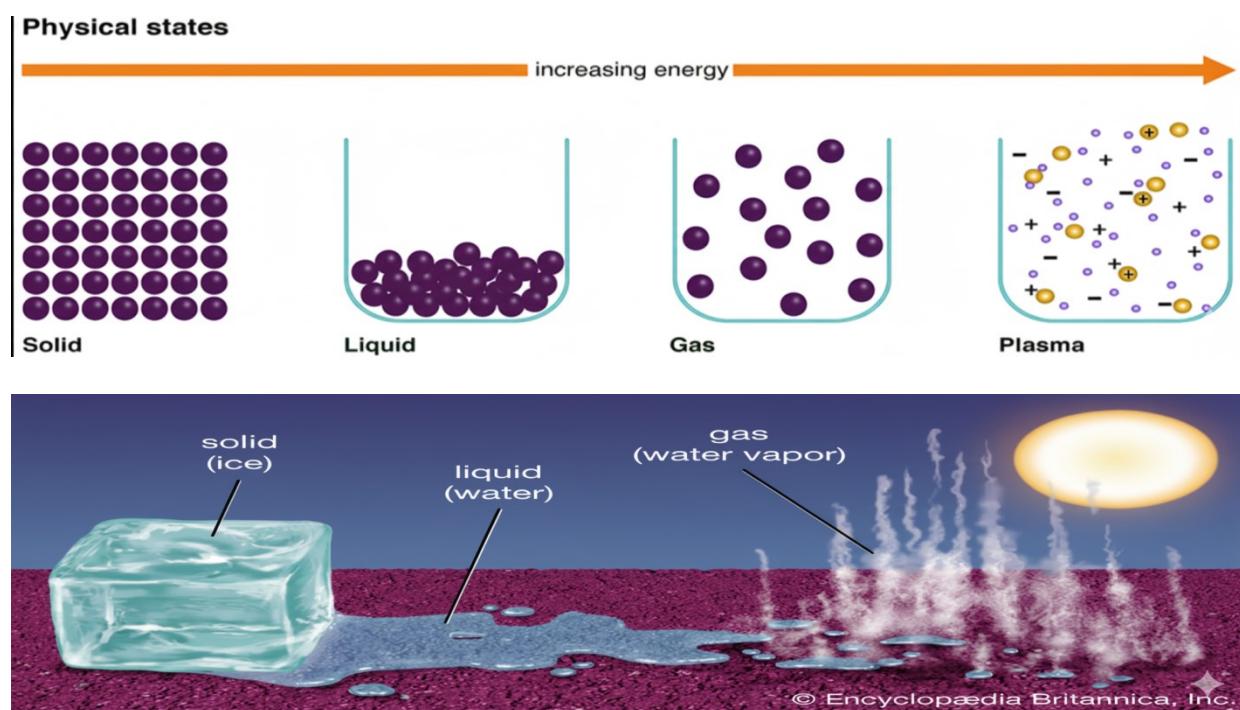

Solids are characterized by an extended three-dimensional arrangement of atoms, ions, or molecules in which the components are usually locked in their positions. Two structures of solids are distinguished:

- **Amorphous structure:** amorphous solids are not arranged in regular lattices or the atoms are organized in a disorderly manner.

- **Crystal structure:** crystalline solids have regular ordered arrays of atoms held together by uniform intermolecular forces. Otherwise, The crystalline state corresponds to an ordered arrangement of atoms or molecules that constitute the solid. There are two types of crystalline solid: Monocrystalline and Polycrystalline.

**Figure 1.2:** Schematic of the three basic structures of crystals: **a)** amorphous, **b)** polycrystalline and **c)** monocrystalline.

**Noticed:**

In liquid crystals, the order is partial: only the order resulting from the orientation of the molecules is preserved, while the geometric arrangement of the molecules in space is, as in any liquid phase, disordered. All bodies in nature are made up of molecules and atoms.

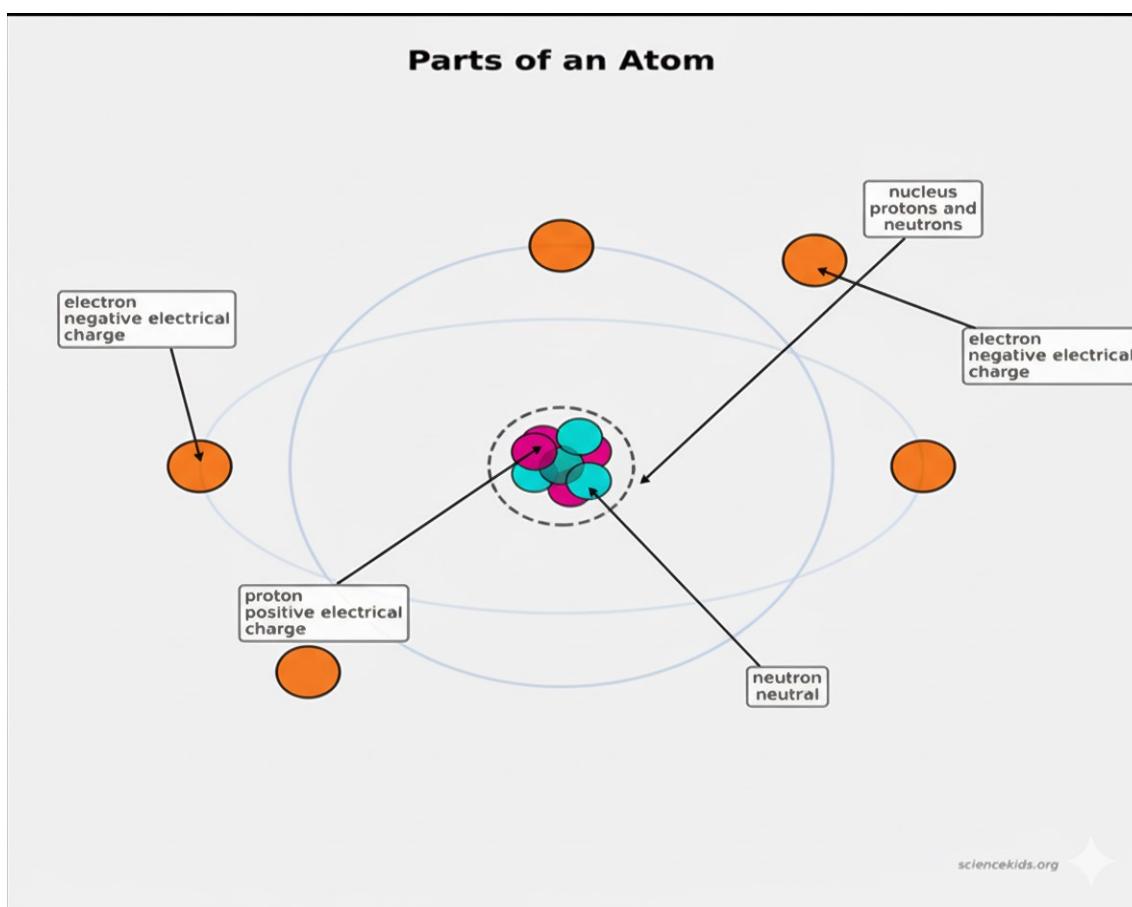

**Figure 1.3:** Representation of parts of atom

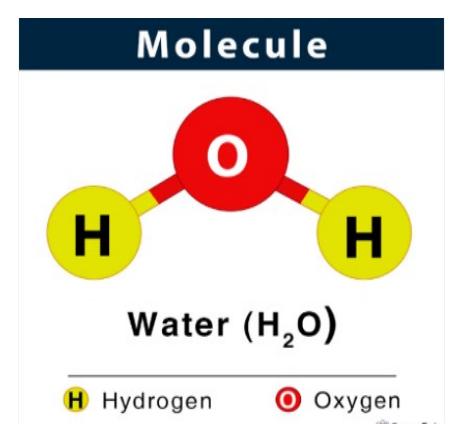

- ◎ **The molecule:** is the smallest particle of the body that can be obtained in the free state (around 10-6mm). The molecules are not immobile. A molecule can be monatomic (formed by a single atom). More generally, it will contain several atoms.

- ◎ **The atom:** is the smallest particle of an element that can enter into the composition of a molecule.

- ◎ **The electron:** is a stable particle of mass:  $9,109 \times 10^{-28}$  g and negative charge equal to  $1,6 \times 10^{-19}$  Cb.

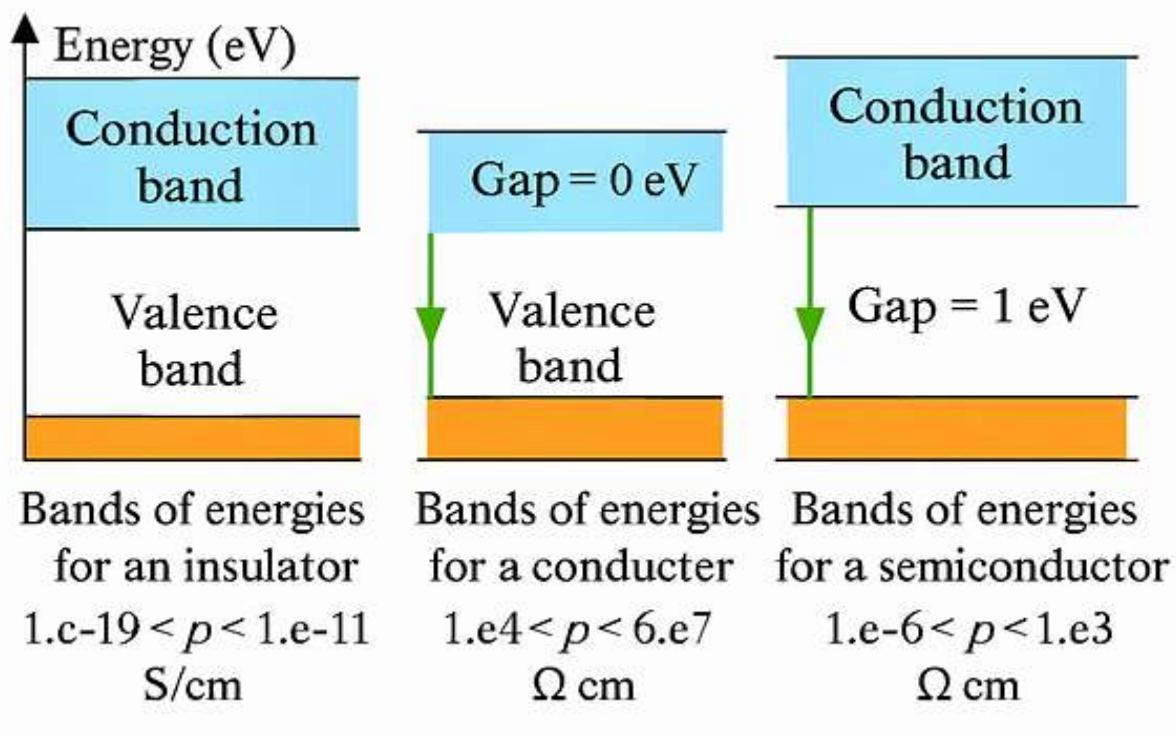

- ◎ **Resistivity:** is the unit that measures the property of bodies to have free electrons in the conduction band. It is expressed in Ohm-meters.

◎ **Conductivity:** Electrical conductivity or specific conductance is defined as the inverse of resistivity. It is a measure of the amount of electrical current a material can carry or its ability to carry current.

**"Conductivity is an intrinsic property of a material."**

Based on the order of magnitude of resistivity or conductivity, solid materials can be classified into three categories: conductors, semiconductors, and insulators. In this course we are interested in the physics of semiconductors classified as crystalline solids while detailing their properties and characteristics.

**Example:** The conductors have a resistivity of the order of  $\mu\Omega\cdot\text{cm}$ , insulators:  $10^{18}\Omega\cdot\text{cm}$  and for semiconductors: it is of the order of  $\Omega\cdot\text{cm}$

**Copper:**  $1,7 \times 10^{-8} \mu\Omega\cdot\text{cm}$ ; **Gold:**  $2,4 \times 10^{-8} \mu\Omega\cdot\text{cm}$

## 1.1 Atomic bonds

### 1.1.1 Definition

Chemical bonding is at the very heart of chemistry. Bonding forces determine most of the enthalpy component of the thermodynamic driving forces for reactions and control key features of molecular structure and properties. When two atoms bond together, they can form a molecule. This bond is called a primary bond. Depending on the degree of interaction between the atoms, one of several states can form.

- In the gaseous state: there is little or no resistance to the movement of atoms or molecules.

- In the liquid state: the resistance is much greater but the molecules can move with ease and facility.

- In the solid state: the movement of atoms is restricted to localized vibrations while other movements by diffusion are possible.

### 1.1.2 Origin of atomic bonds

All bonds have a common origin: the electrostatic attraction between the positive charges of the atomic nucleus and the negative charges of the electrons. There are attractions and repulsions between the electric charges of the electrons and the nuclei. American chemist-physicist **Gilbert Newton Lewis** (1875-1946) played a pivotal role in the development of covalent bond theory. In 1916, he published his seminal paper suggesting that a chemical bond is a pair of electrons shared by two atoms.

Gilbert N. Lewis

1875 - 1946

The quantum origins of the forces that hold atoms tightly and strongly together have been the subject of intense moved beyond pre-quantum concepts such as "hooks and eyes" to Lewis shared electron pairs. [Daniel S. Levine & Martin Head-Gordon]

The balance between the forces of electrostatic repulsion and attraction leads to the existence of an equilibrium distance between two atoms, characteristic of the bond considered.

### 1.1.3 Types of atomic bonds

However, for atoms to form crystals, there must be an attractive force between them. This force is called **Van der Waals** attraction. Atomic bonds are of several types. Let us mention the two main ones:

#### i. **Ionic or electrovalent bond:**

In 1884, Svante August Arrhenius reasoned that an ion is actually an atom carrying a positive or negative charge. He proposed that a compound like sodium chloride would break into ions when dissolved in water, whether or not an electric current was present.

Johannes Diderik van der Waals

1837 - 1923Svante A. Arrhenius

1859 - 1927

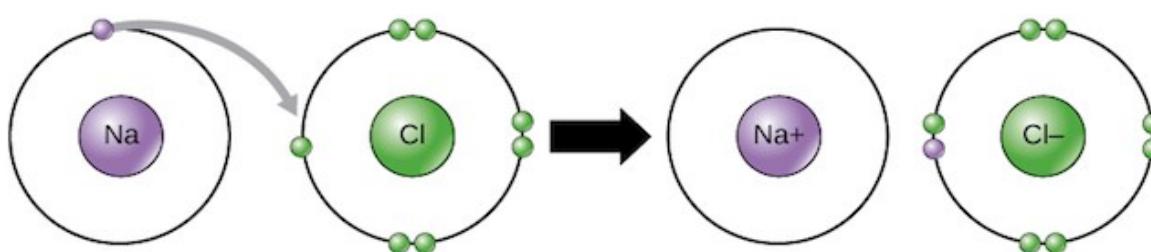

ii. **Ionic bonding:** is based on the effective transfer of one to more than one electron from the outermost layer of the strong metal to the outermost layer of the strong non-metal; the metal is the potential donor of electron(s), the non-metal the acceptor. An ionic combination is the association of ions called **anions** and **cations** which attach to the vicinity of each other by Coulomb attraction.

Ionic bond = strong metal + strong non-metal.

**Noticed:** “Strong metal like Cesium and strong non-metal like Fluorine”.

(see Dmitri Ivanovich Mendeleev's periodic table)

**Example:** Taking the example of Sodium Chloride where chlorine has seven (07) peripheral electrons while sodium only has one.

- **Na<sup>+</sup>** as a positive ion since the Sodium atom loses a peripheral electron.

- **Cl<sup>-</sup>** as a negative ion because the Chlorine atom recovers the electron torn from the sodium.

- Generally speaking, the loss of an electron by one atom and the gain of an electron by another atom must occur at the same time: for a sodium atom to lose an electron, it must have a suitable receptor, such as a chlorine atom. Each of these atoms ends up with a complete outer shell. It is electrostatic forces that hold the whole thing together.

- Ionic or electrovalent interactions are generally observed in neutralization reactions between acids and bases. Thus, most ionic compounds are salts

Image credit: OpenStax Biology.

**Figure 1.4:** Formation of the ionic bond

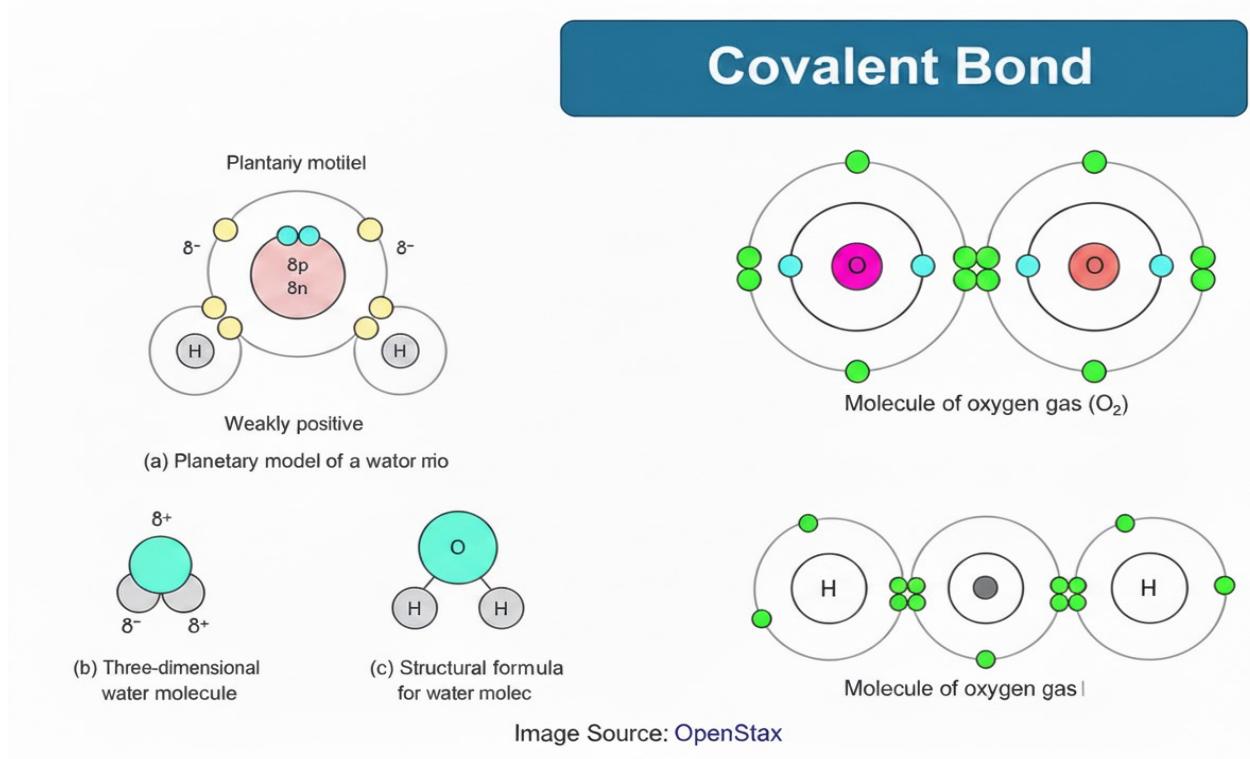

iii. **Covalent bond:**

Covalent bond = one non-metal + one non-metal.

This is the case for semiconductors and insulators. For silicon, each atom is at the center of a tetrahedron whose four vertices are four other identical atoms. The permitted layers are transformed into bands or zones composed of several distinct but very close layers.

The goal of the covalent bond is to achieve a stable electronic configuration for the two atoms involved. The movement of an electron from one layer to another towards the outside is carried out in a discrete way (by jumps) if additional energy is communicated to it (by heating for example). The return is also possible and is accompanied by a release of energy.

**Figure 1.5:** Representation of covalent bond

Generally, ionic bonds are much stronger than covalent bonds. In ionic bonds, there is a complete transfer of electrons between elements to form a stable compound. In covalent bonds, there is only one sharing of electrons between two elements to form a stable compound.

## 1.2 Crystalline solid state

As mentioned above, crystals are a collection of atoms arranged in a certain order. Since the atom is not isolated (it is part of the crystal), its electrons are influenced by neighboring atoms.

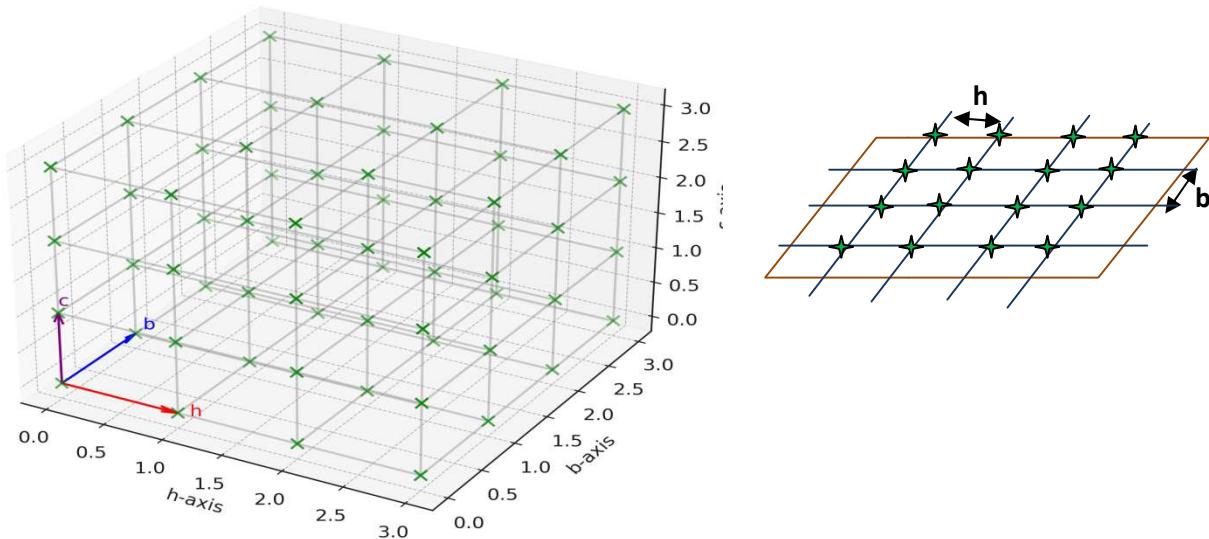

### 1.2.1 Point-lattice

It is made up of a set of points (the green points) placed periodically on which atoms or molecules called: motifs would be placed. Therefore the set point **lattice** + **motif** = **crystal lattice**. Examples of motifs include: Silicon (Si), Germanium (Ge) or Gallium Arsenide (GaAs) as a binary motif. A crystal lattice is made up of the regular reproduction of a molecule AB or an atom A called: motif or base.

3D Crystal Lattice with Basis Vectors

**Figure 1.6:** Representative diagram of the crystal lattice

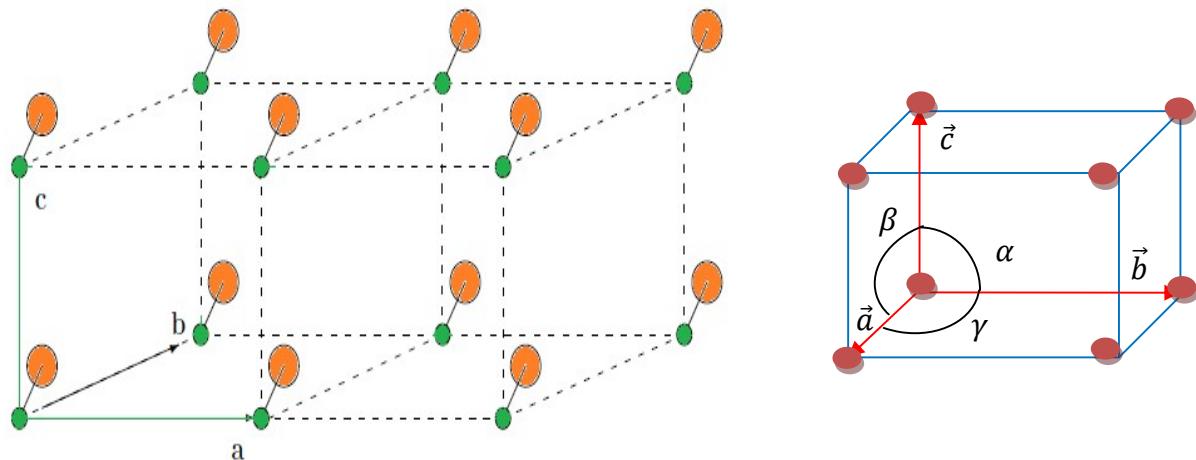

### 1.2.2 Definition

In a crystal lattice we define a reference  $(0, \vec{a}, \vec{b}, \vec{c})$ .  $\vec{a}, \vec{b}, \vec{c}$  are the direction vectors that join two consecutive nodes. The parallelepiped formed on these vectors is called an elementary cell. The latter can only contain one node. The node is the smallest part allowing the reconstitution of the crystal. It can be described by the direction vectors  $\vec{a}, \vec{b}, \vec{c}$  as well as the angles:  $\alpha, \beta, \gamma$ . A cell is said to be conventional if it contains at least two nodes

$$v_c = v_c \cdot k$$

**Figure 1.7:** Representation of the cubic lattice

### 1.2.3 The Bravais lattices

In 1948 Bravais demonstrated that three-dimensional space has a lattice number equal to 14 to explain all crystals. They are called direct and are grouped into 7 systems. The primitive lattice, the base-centered lattice, the body-centered lattice and the face-centered lattice are the four types of Bravais lattices. Among these systems, the most important are the cubic, hexagonal and rhombohedral systems. The cubic system is formed by three lattices.

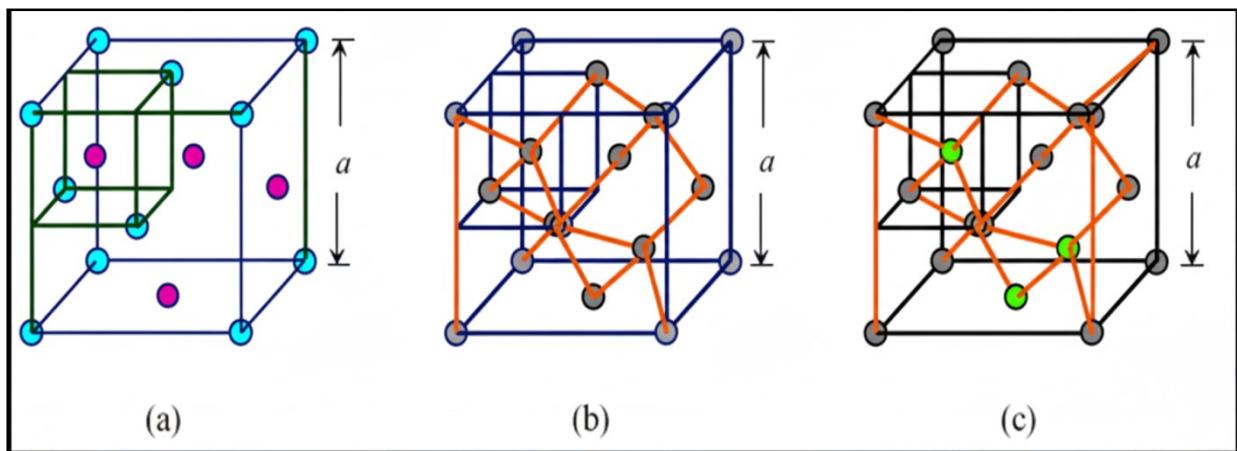

**Figure 1.8** **a)** Face-centered cubic lattice, **b)** Diamond lattice: obtained by moving the lattice atoms of a) by  $(a/4, a/4, a/4)$ , **c)**: Zinc-blend structure: when the displaced lattice atoms are different from the original lattice atoms.

#### 1.2.4 Reticular plane and index

**Definition 1:** We group all the nodes of a lattice on a plane called the reticular or crystallographic plane.

**Definition 2:** All the nodes can be gathered on a parallel line called a reticular line or crystallographic line.

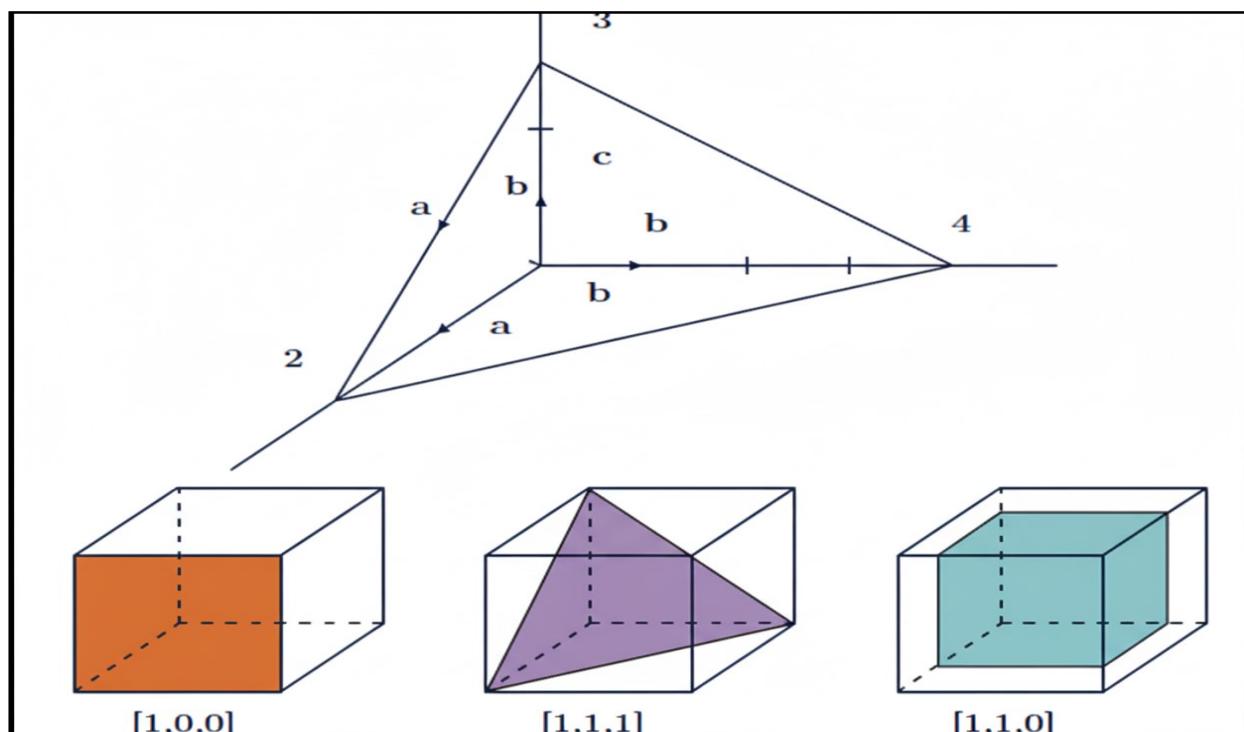

**Definition 3:** Some families of direction or plans are identified by indices called: Miller indices.

#### 1.2.5 Miller direction indices

Let  $(a, b, c)$  be the fundamental vectors of a crystal lattice. If  $\vec{v} = h\vec{a} + k\vec{b} + l\vec{c}$ , is the crystallographic direction vector. Therefore, the Miller indices are deduced as follows:

$$\vec{v} = -\vec{a} + \frac{3}{4}\vec{b} + \frac{1}{2}\vec{c} \rightarrow \left[1, \frac{3}{4}, \frac{1}{2}\right] \rightarrow \left[-\frac{4}{4}, \frac{3}{4}, \frac{2}{4}\right] \rightarrow [-4, 3, 2] \rightarrow [4, 3, 2] \quad (1.1)$$

### 1.2.6 Miller plan indices

Let be a vector:  $v = hx + ky + lz$ . The Miller indices of the design are determined as follows:

$$t = 2a + 3b + 4c \rightarrow (2,3,4) \rightarrow \left(\frac{1}{2}, \frac{1}{3}, \frac{1}{4}\right) \rightarrow \left(\frac{6}{12}, \frac{4}{12}, \frac{3}{12}\right) \rightarrow (6,4,3) \quad (1.2)$$

$[a, b, c]$  : Miller index of direction

$(a, b, c)$  : Miller index of plan

$\langle a, b, c \rangle$  : Miller index of direction group

$\{a, b, c\}$  : Miller index of plan group.

If  $(h, k, l)$  are coprime, they characterize the Miller indices of direction or plane or a group of direction or plane. Any index direction  $[h, k, l]$  is perpendicular to the plane of the same index  $(h, k, l)$ .

**Figure 1.9:** Miller indices of the drawn plane & the 3 most common lattice planes for cubic lattices.

### 1.2.7 Reciprocal lattice

In physics, two lattices are often associated with each crystal structure: direct lattice and reciprocal lattice. The Bravais lattice corresponds to the real space where the fundamental vectors corresponding to lengths are:  $\vec{a}, \vec{b}, \vec{c}$ . The reciprocal lattice corresponds to the space of wave vectors:  $\vec{A}, \vec{B}, \vec{C}$ . These represent the reciprocal parameters of the reciprocal lattice. Their dimension is  $L^{-1}$  and they are described by the equations below:

$$\vec{A} = \frac{2\pi(\vec{b} \wedge \vec{c})}{\vec{a} \cdot \vec{b} \wedge \vec{c}} \quad (1.3)$$

$$\vec{B} = \frac{2\pi(\vec{a} \wedge \vec{c})}{\vec{b} \cdot \vec{c} \wedge \vec{a}} \quad (1.4)$$

$$\vec{C} = \frac{2\pi(\vec{a} \wedge \vec{b})}{\vec{c} \cdot \vec{a} \wedge \vec{b}} \quad (1.5)$$

## 1.3 Defects in crystals

The perfect semiconductor single crystal is dull compared to the wide variability of today's deliberately designed materials. The ideal model for a solid requires unintelligible translational symmetry. Each atom resides at its prescribed site; no impurities or defects are permitted. Real crystals are not perfect and have defects. These are sometimes beneficial and introduced deliberately to modify the properties of materials (electrical, optical, crystallographic, etc.). Defects or imperfections in crystalline solids can be divided into four groups, namely point defects, linear (1D or line) defects, surface (2D) defects, and volume (3D) defects.

### 1.3.1 Point defects

They are involved in certain phenomena such as the diffusion of foreign atoms in crystals. Generally speaking, these defects are generated in metals and ionic crystals.

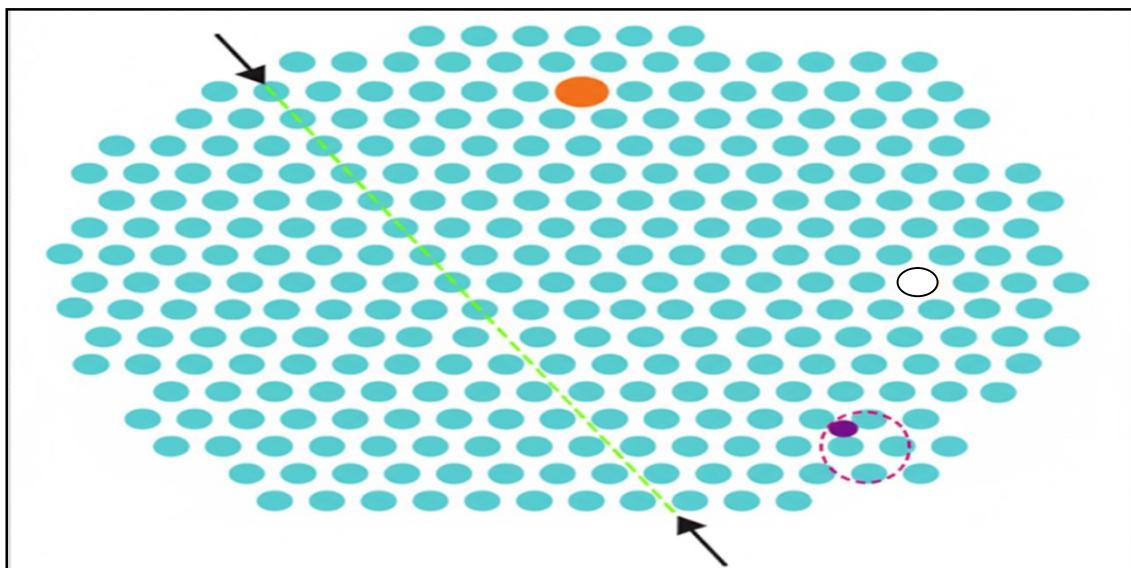

**Figure 1.10:** Representation of point and line defects

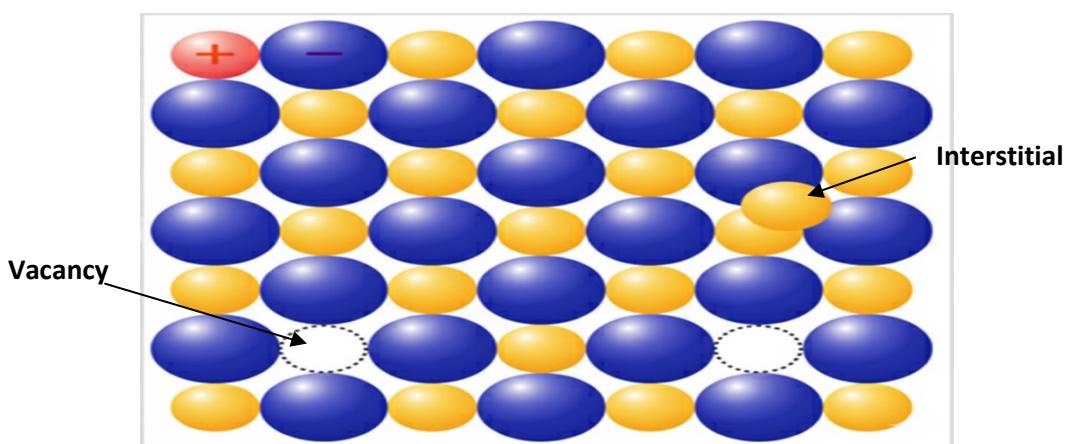

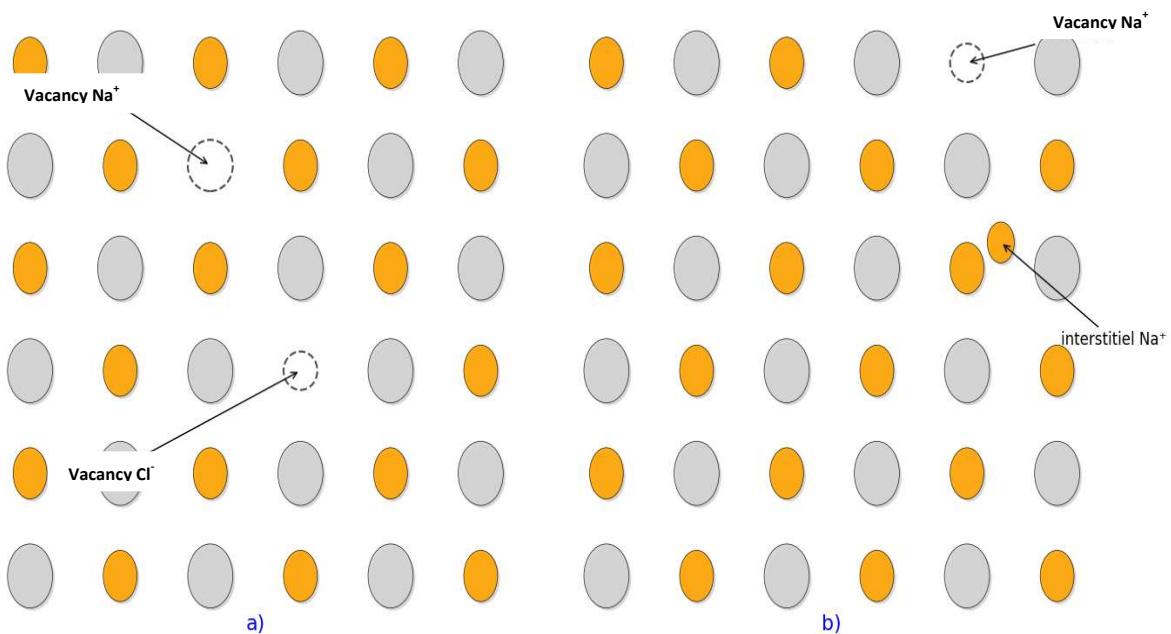

### 1.3.2 Vacancy and interstitial

A vacancy is the absence of an atom from the crystal lattice, while an interstitial is an atom in the lattice that is no longer in its position. Under the effect of thermal agitation, some atoms acquire sufficient energy to leave their places by tilting neighboring atoms and to accommodate themselves more or less from their defect positions. They would therefore be in an "interstitial" position, commonly called a Fränkel defect.

**Noticed:** Vacancies can occur without being accompanied by interstitials defects.

**Figure 1.11:** Representation of defects: vacancy and interstitial

The presence of two oppositely charged vacancies is called a Schottky defect, while the formation of a vacancy-interstitial pair is called a Schottky defect. Fränkel).

**Figure 1.12:** Representation of **Fränkel** and **Schottky** defects:

- a) Presence of two oppositely charged vacancies (Schottky defect)

- b) Formation of a vacancy-interstitial pair (lack of Fränkel)

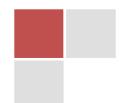

### 1.3.3 Non-point geometric defects (Dislocations or line)

When a crystal is subjected to pressure, it will undergo deformations which can be: elastic, plastic or fractures. These deformations imply the existence of low resistance surfaces through which the crystallographic planes can slide.

**Figure 1.13:** Representation of line defects (dislocation)

### 1.3.4 Composition defects

#### i. Impurity Defects

These defects are due to foreign atoms incorporated into the crystal in substitution or interstitial positions acting on the properties of the crystal. They must therefore be purified (pure semiconductor is therefore an intrinsic semiconductor).

#### ii. Additive or doping defects

These defects are due to the doping process which subsequently modifies the properties of the crystal, particularly its conductivity. These defects depend on the type of doping: donor or acceptor.

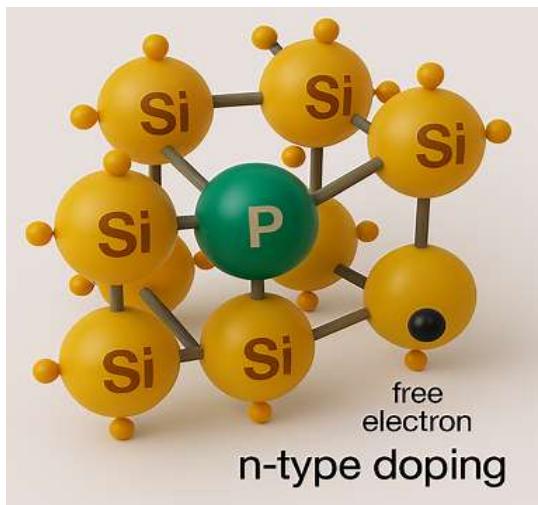

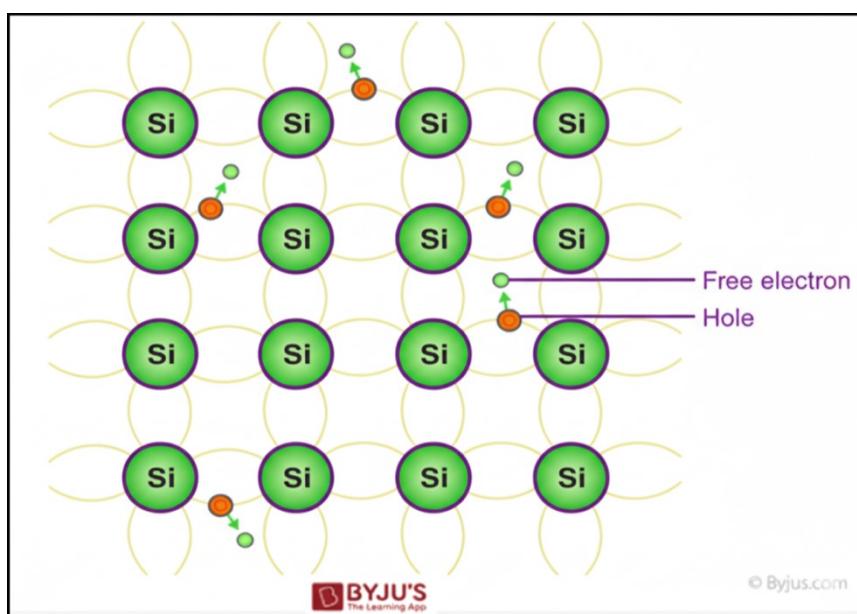

##### a. Donors

When we introduce donor atoms into a crystal (atoms in the 5<sup>th</sup> column of the periodic table of materials like Phosphorus and arsenide), the crystal is therefore said to be of type N. In this case (04) electrons of the peripheral layer (last filled layer) form covalent bonds with 04 electrons of silicon. The 5th electron

participates in conduction (by electron). So the donor atoms release an electron into the crystal lattice. The donor atoms create an energy level close to the valence band.

Each phosphorus atom releases an electron into the lattice

| Symbol | Name       | Atomic Number | Atomic Mass |

|--------|------------|---------------|-------------|

| N      | Nitrogen   | 7             | 14.006855   |

| P      | Phosphorus | 15            | 30.973762   |

| As     | Arsenic    | 33            | 74.92160    |

| Sb     | Antimony   | 51            | 121.760     |

Figure 1.14: Simplified representation of N-type doping

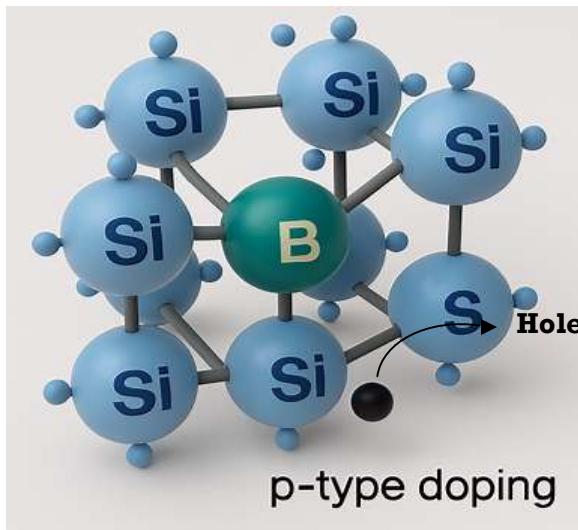

### b. Acceptor

When acceptor atoms are introduced into a crystal (silicon for example): atoms from the 3<sup>rd</sup> column of the periodic table of materials such as Boron or gallium, the crystal is therefore said to be of type P. In this case, three (03) electrons only from the peripheral layer (last filled layer) form covalent bonds with three (03) electrons from silicon. An electron-hole pair is released into the lattice (electron from silicon and hole from Boron). Therefore the acceptor atoms release a hole into the crystal lattice and conduction is done by hole.

| Symbol | Name     | Atomic Number | Atomic Mass |

|--------|----------|---------------|-------------|

| B      | Boron    | 5             | 10.81       |

| Al     | Aluminum | 13            | 26.9815385  |

| Ga     | Gallium  | 31            | 69.723      |

| In     | Indium   | 49            | 114.818     |

**Figure 1.15:** Simplified representation of P-type doping

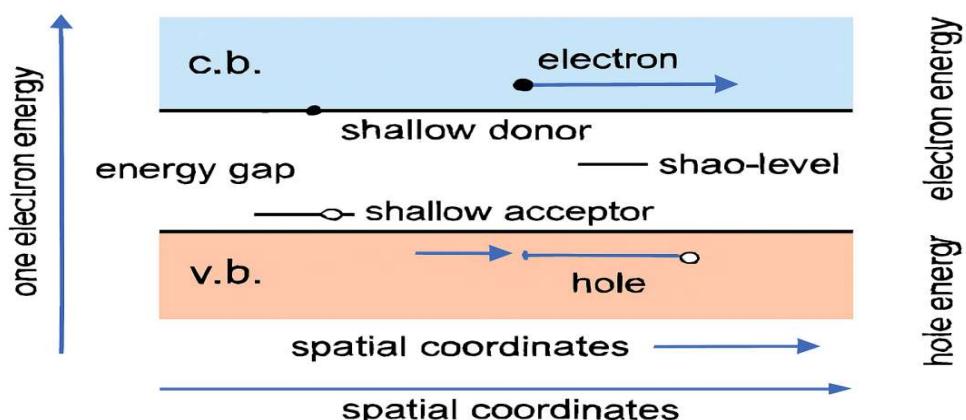

### c. Deep defects

In the case of silicon, deep defects appear during the thermal processing of wafers with disordered surfaces. This disorder is the result of mechanical lapping or the introduction of high-concentration impurities into the diffusion layer. Alternatively, deep-level defects are defects positioned deeper in the band gap than dopant levels (shallow donor and acceptor dopants) and bind much more strongly to carriers in tightly packed localized states. Deep levels have higher ionization energies and therefore contribute very little to free charge carriers.

**Figure 1.16:** Schematic representation of the energy levels created by deep defects and by dopants.

## 1.4 Energy band theory in crystals

The study of band theory aims to understand the electrical properties of free charges. In this section, we will outline the principles related to energy bands for an isolated atom and an atom in the crystal lattice. In order to calculate the energy band structures of a semiconductor, it is necessary to:

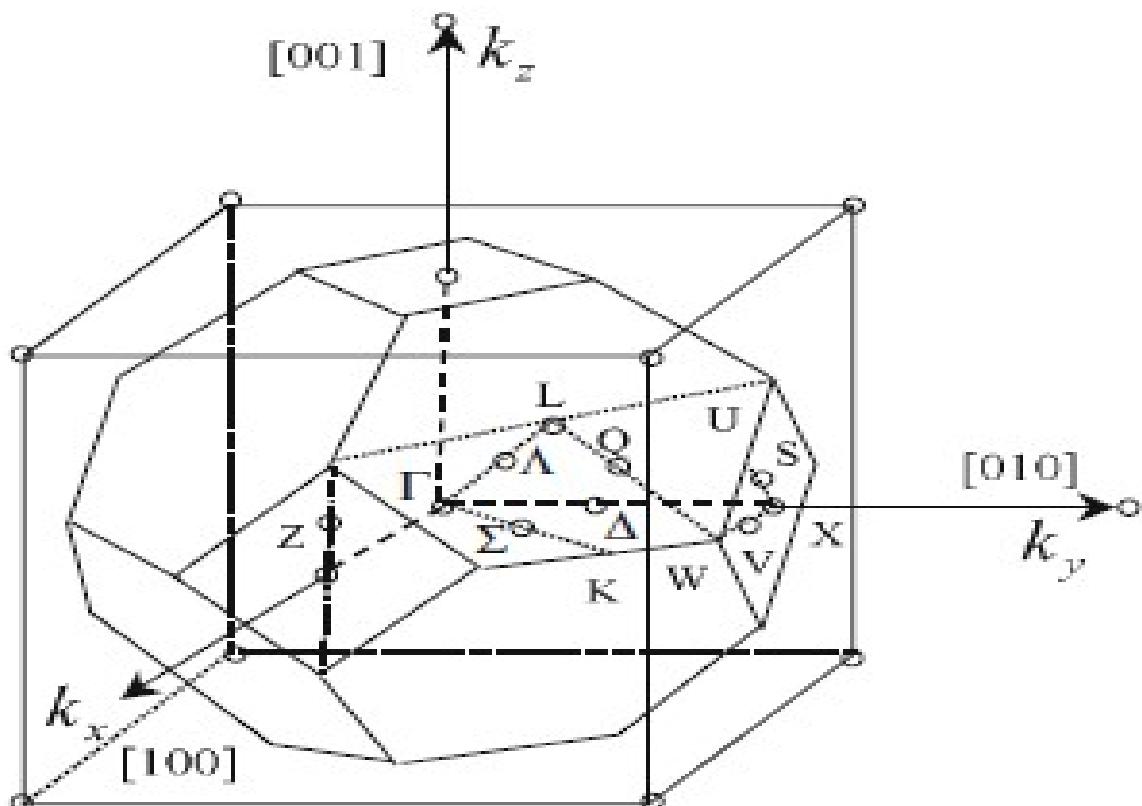

- Calculate the first Brillouin zone.

- Calculate the energy band structures in the limit of zero potential energy.

- Then calculate the energy bands using an appropriate method.

**Figure 1.17:** Brillouin zone of a face-centered cubic lattice.

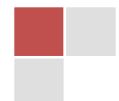

**Figure 1.18:** Examples of energy band structures calculated by the K.p perturbation method: a) Germanium b) Silicon

## 1.5 Energy bands and level density

### 1.5.1 Electrical analogy: LC circuit

Consider the LC circuit in the figure opposite. We propose to determine the oscillation frequency of the circuit.

$$\frac{q}{c} + \frac{q}{c_1} + L \frac{d^2q}{dt^2} = 0 \quad (1.6)$$

The solution is of the form:  $q(t) = K \sin(\omega t + \varphi)$

$$\left( L\omega_0^2 - \frac{1}{c} + \frac{1}{c_1} \right) q = 0 \rightarrow \omega_0 = \sqrt{\frac{1}{L} \left( \frac{1}{c} + \frac{1}{c_1} \right)} \quad (1.7)$$

2<sup>nd</sup> case:

$$\begin{cases} L \frac{d^2q_1}{dt^2} + \frac{q_1}{c} + \frac{q_1+q_2}{c_2} = 0 \\ L \frac{d^2q_2}{dt^2} + \frac{q_2}{c_1} + \frac{q_1+q_2}{c_1} = 0 \end{cases} \quad (1.8)$$

With:  $q_1 = A_1 \sin(wt + \varphi_1)$ ,  $q_2 = A_2 \sin(wt + \varphi_2)$

$$\begin{cases} \left( -L\omega^2 + \frac{1}{c} + \frac{1}{c_1} \right) q_1 + \frac{q_2}{c} = 0 \\ \left( -L\omega^2 + \frac{1}{c} + \frac{1}{c_1} \right) q_2 + \frac{q_1}{c} = 0 \end{cases} \quad (1.9)$$

$q_1$  and  $q_2$  are the roots of the system, the only solution is  $q_1 = q_2 = 0$ , or  $q_1$  and  $q_2 \neq 0$ , so it is the determinant is equal to 0.

$$\left( -L\omega^2 + \frac{1}{c} + \frac{1}{c_1} \right)^2 = \left( \frac{1}{c_1} \right)^2 \rightarrow L\omega^2 = \frac{1}{c} + \frac{1}{c_1} \pm \frac{1}{c_1} \quad (1.10)$$

So

$$\omega^2 = \omega_0^2 \pm \frac{1}{Lc_1}, \quad \omega_0^2 = \frac{1}{Lc} + \frac{1}{Lc_1} \quad (1.11)$$

The simple LC circuit oscillates with a single frequency, if it is added to another circuit there will be a 2<sup>nd</sup> frequency. The oscillation frequency of the electrical system is analogous to the electrical energy in another.

### 1.5.2 The energy levels of electrons in the isolated atom

In an isolated atom, electrons can only occupy discrete energy levels. The electrons occupy circular orbits of radius  $r_n$  to which potential energies  $V$  are associated (crystalline potential). These electrons occupy the orbits closest to the nuclei. The electrons in the outermost shell are the valence electrons least bound to the nucleus.

$$r_n = n^2 \epsilon_0 \frac{ln^2}{\pi m q^2} \quad (1.12)$$

$$V_c(r) = V_c(r + T) \quad (1.13)$$

$$V = \frac{q^2}{4\pi\epsilon_0 r} \quad (1.14)$$

With  $T$  represents the translation vector of the crystal lattice.

The periodicity of the crystal potential results in a fundamental property of the electron wave function given by the **Bloch's theorem**.

### 1.5.3 Energy structure of the crystal

#### a. Definition

In a crystal, electrons are arranged in a perfectly periodic manner; they are not independent but coupled instead of each single level of the isolated atom. We have "n" energy levels.

- 2 The valence band (VB): this is the last permitted energy band occupied by electrons at (0K)

- 3 The conduction band (CB): this is the first empty band of electrons at (0K). When passing from the CB to the CB, the electron leaves behind a hole.

The energy band that separates the valence band from the conduction band is called the forbidden band or gap characterized by an energy  $E_g$ . This energy allows us to classify it as a semiconductor, insulator or conductor.

**Figure 1.19:** Representation of energy bands in an insulator, conductor and semiconductor.

**b. Notion of hole**

In a semiconductor material, at temperature of **zero Kelvin**, all electrons are in the valence band. The material is considered an insulator. If the temperature increases, the electrons can reach the BC. In this case, the electrons leave in their place voids called holes. The latter are positively charged and can be occupied by other electrons. We talk of hole conduction in the valence band and electron conduction in the conduction band. Let the crystals contain "**n**" atoms at a particular possible energy whose isolated atom will correspond to a group **n** of possible energies which are all the more important than the initial level as the interaction between the electrons is strong. The possible energies for an electron in a solid form permitted bands (PB) separated by forbidden bands.

**c. Density of levels in a permitted band**

For an electron to move from the valence band to the conduction band, it must be supplied with energy  $\geq E_g$ , and  $D_E$  which is defined as the level density. It is zero outside the permitted bands. For an atom isolated in space, the energy levels of its different electrons are perfectly determined by the quantum numbers N, L, M. In accordance with the "**Pauli exclusion principle**", each level can be occupied by only two electrons, with opposite spins. In a crystal, the energy levels are then divided into AA permitted bands', BB', intervals such as A'B' being forbidden bands. In this bringing together of atoms and the decomposition of levels, it may happen that the allowed bands overlap or not.

## Chapter II: Electronic transport in semiconductors

### Introduction

The study of electronic transport in semiconductors and solids in general is essential in determining the electrical properties of both semiconductors and components. Transport is an intrinsically non-equilibrium phenomenon, where the role of dissipation and coupling to the environment play a crucial role. In this chapter, we discuss the charge transport mechanisms and the different currents flowing in a semiconductor.

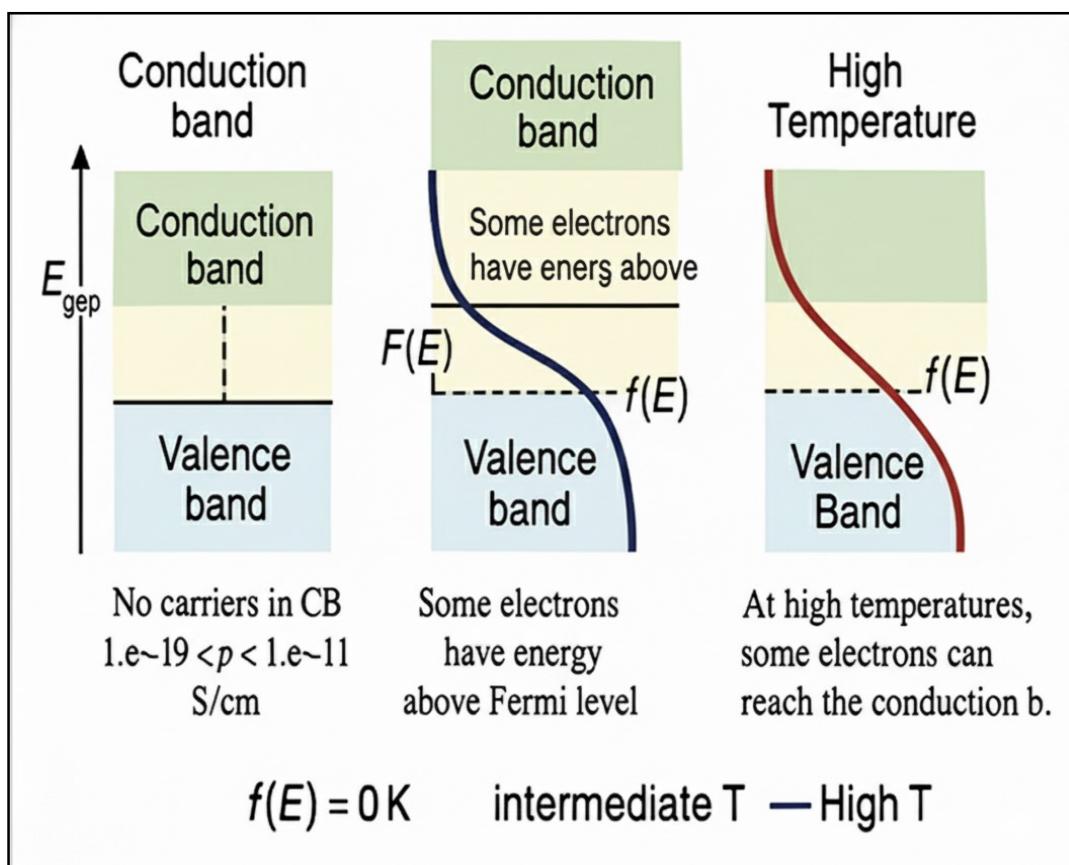

#### 2.1. Population of energy levels: at thermodynamic equilibrium

Knowing the band structure as well as the localized quantum levels (introduced into the band gap by impurities), it would be necessary to determine their distribution across the authorized energy levels (the allowed bands) while evaluating the conductivity of electrons and holes. However, knowledge of the position and the exact kinetic energy associated with each electron remains impossible. For this we resort to statistical methods and probability laws.

##### 2.1.1. Concepts of probability of occupation of an energy level $E$

According to the Pauli exclusion principle there can only be 1 or 2 electrons per quantum level. Given the Pauli exclusion principle, we must therefore know what probability  $f(E)$  exists for a crystal electron to have occupied an energy level  $E$ . In static thermodynamics it is shown that for the electrons of the crystal we can apply the Fermi-Dirac statistics.

According to this statistic, the electrons of a crystal are assimilated to an electronic gas such that:

$$f(E) = \frac{\text{nombre de places occupées}}{\text{nombre de places occupables}}$$

### 2.1.2. In the case of electrons

$$f_n(E) = \frac{1}{1 + \exp\left(\frac{E-E_F}{KT}\right)} \quad (2.1)$$

$f_n(E)$  : Probability that an energy level  $E$  is occupied by an electron at thermodynamic equilibrium.

$E_F$  : is a reference level called the Fermi level defined as the last occupied level at 0K.

$K = 8,62 \times 10^{-5} \text{ eV/K}$  is the Boltzmann constant and  $T$  temperature in Kelvin (K)

### 2.1.3. In the case of holes

The probability function that an energy level  $E$  is occupied by a hole is given by the following expression:

$$f_p(E) = 1 - f_n(E) = 1 - \frac{1}{1 + \exp\left(\frac{E-E_F}{KT}\right)} \quad (2.2)$$

$$f_p(E) = \frac{1}{1 + \exp\left(\frac{E_F-E}{KT}\right)} \quad (2.3)$$

The fundamental nature of the distribution function dictates that at ordinary temperatures, most levels up to the Fermi level  $E_F$  are filled, and relatively few electrons have energies above the Fermi level.

The Fermi level is on the order of electron volts, whereas the thermal energy “**KT**” is only about 0,026 eV at 300K. So if we put these numbers into the Fermi function at ordinary temperatures, we find that its value is essentially 1 up to the Fermi level and quickly approaches zero above it.

The illustration below shows the implications of the Fermi-Dirac function for the electrical conductivity of a semiconductor. The band theory of solids shows that there is a large gap between the Fermi level and the conduction band of the semiconductor. At higher temperatures, a larger fraction of electrons can bridge this gap and participate in electrical conduction.

**Figure 2.1:** Illustration of the implication of the Fermi-Dirac function for the electrical conductivity of a semiconductor.

## 2.2. Calculation of charge carrier concentrations in the permitted bands

Charge carriers are the free electrons in the conduction band and the free holes in the valence band.

### 2.2.1. Concentration of free electrons in the conduction band

The concentration of electrons is defined as follows:

$$n = \int_{E_c}^{+\infty} \frac{dn}{dN} \cdot \frac{dN}{dE} \cdot dE = \int_{E_c}^{+\infty} f_n(E) \cdot D_c(E) \cdot dE \quad (2.4)$$

$$D_c(E) = \frac{4\pi}{h^3} (2m_n^*)^{\frac{3}{2}} (E - E_c)^{\frac{1}{2}} \quad (2.5)$$

So :

$$n = \int_{E_c}^{+\infty} \frac{1}{1 + \exp(\frac{E - E_F}{KT})} \frac{4\pi}{h^3} (2m_n^*)^{\frac{3}{2}} (E - E_c)^{\frac{1}{2}} \cdot dE \quad (2.6)$$

We make the following approximation:  $E \gg KT$

We obtain:

$$n = \frac{4\pi}{h^3} (2m_n^*)^{\frac{3}{2}} \int_{E_c}^{+\infty} \exp\left(\frac{E_F - E}{KT}\right) (E - E_c)^{\frac{1}{2}} \cdot dE \quad (2.7)$$

We ask:

$$A = \frac{4\pi}{h^3} (2m_n^*)^{\frac{3}{2}} \quad \text{And} \quad E_F - E = (E_F - E_c) + (E_c - E) = (E_F - E_c) - (E - E_c)$$

$$n = A \int_{E_c}^{+\infty} \exp\left[\frac{(E_F - E_c) + (E_c - E)}{KT}\right] (E - E_c)^{\frac{1}{2}} \cdot dE \quad (2.8)$$

$$n = A \cdot \exp\left(\frac{E_F - E_c}{KT}\right) \int_{E_c}^{+\infty} \exp\left(-\left(\frac{E - E_c}{KT}\right)\right) \cdot (E - E_c)^{\frac{1}{2}} \cdot dE \quad (2.9)$$

$$\text{Posing: } U = \frac{E - E_c}{KT}; \quad (E - E_c)^{\frac{1}{2}} = \left(\frac{E - E_c}{KT}\right)^{\frac{1}{2}} \cdot (KT)^{\frac{1}{2}}$$

$$n = A \cdot \exp\left(\frac{E_F - E_c}{KT}\right) (KT)^{\frac{1}{2}} \int_{E_c}^{+\infty} \exp(-U) \cdot (U)^{\frac{1}{2}} \cdot dU \cdot KT \quad (2.10)$$

To determine the concentration  $n$  we use the following theorems:

$$\begin{cases} \gamma(x) = \int_0^{+\infty} t^{x-1} e^{-t} dt \\ \gamma(x+1) = x\gamma(x) \\ \gamma\left(\frac{1}{2}\right) = \sqrt{\pi} \end{cases} \quad (2.11)$$

We then obtain:  $n = \frac{4\pi(KT)^{\frac{3}{2}}}{h^3} (2m_n^*)^{\frac{3}{2}} \exp\left(\frac{E_F - E_C}{KT}\right)$  (2.12)

By identification:  $x - 1 = \frac{1}{2} \rightarrow x = 1 + \frac{1}{2}; \quad \gamma\left(1 + \frac{1}{2}\right) = \frac{1}{2}\gamma\left(\frac{1}{2}\right) = \frac{\sqrt{\pi}}{2}$

$$n = \frac{4\pi}{h^3} (2KTm_n^*)^{\frac{3}{2}} \exp\left(\frac{E_F - E_C}{KT}\right) \quad (2.13)$$

From where  $\forall T^\circ$ :

$$n = N_C \exp\left(\frac{E_F - E_C}{KT}\right) \quad (2.14)$$

With:  $N_C = \frac{4\pi}{h^3} (2KTm_n^*)^{\frac{3}{2}}$  represents the effective density of state of electrons

### 2.2.2. Concentration of free holes in the valence band

By the same reasoning we determine the concentration of free holes in the valence band such that  $(\forall T^\circ)$ :

$$p = N_V \exp\left(\frac{E_V - E_F}{KT}\right) \quad (2.15)$$

With:  $N_V = \frac{4\pi}{h^3} (2KTm_p^*)^{\frac{3}{2}}$  represents the effective state density of holes.

## 2.3. Classification of semiconductors according to the concentration of charge carriers

### 2.3.1. Intrinsic semiconductor

An intrinsic semiconductor is a chemically pure semiconductor, i.e., one free of impurities. The number of holes and electrons is determined by the properties of the material itself rather than by impurities. Therefore, in intrinsic semiconductors, the number of excited electrons is equal to the number of holes;  $n = p$ .

**Figure 2.2:** Illustration of the intrinsic semiconductors

#### a. Fermi level

In the case of an intrinsic semiconductor, the concentration of electrons is equal to that of holes.  $= p = n_i$

$$N_C \exp\left(\frac{E_{Fi} - E_C}{KT}\right) = N_V \exp\left(\frac{E_V - E_{Fi}}{KT}\right) \quad (2.16)$$

In fact, entering the logarithm on the two terms of the equation gives:

$$\rightarrow \ln \frac{N_C}{N_V} = \frac{2E_{Fi} - E_g}{KT} \quad (2.17)$$

$$E_{Fi} = \frac{E_C + E_V}{2} - \frac{KT}{2} \ln \frac{N_C}{N_V} \quad (2.18)$$

At 300K  $N_C$  and are of the same size  $N_V$ :

$$E_{Fi} = \frac{E_C + E_V}{2} \quad (2.19)$$

**Noticed:** In an intrinsic semiconductor the Fermi level is in the middle of the band gap

### b. Calculation of intrinsic concentration

According to the law of mass action:

$$n \cdot p = n_i^2 \quad (2.20)$$

$$N_C \exp\left(\frac{E_{Fi} - E_C}{KT}\right) \cdot N_V \exp\left(\frac{E_V - E_{Fi}}{KT}\right) = n_i^2 \quad (2.21)$$

$$n_i = \sqrt{N_C N_V} \exp\left(\frac{-E_g}{2KT}\right) \quad (2.22)$$

#### 2.3.2. Extrinsic semiconductor and temperature effect

It is important to emphasize that in an extrinsic semiconductor the number of charge carriers varies with temperature. There are three distinct temperature regions:

##### a. Low temperature region: $T^{\circ} < 100K$

###### ⦿ Case of an N-type semiconductor

At low temperatures, intrinsic ionization is very low. Only the electrons in the conduction band prevent thermal ionization of the donors:

If  $T^{\circ} < 100K$ :

$$n_N = \frac{N_D}{1 + \exp\left(\frac{E_F - E_D}{KT}\right)} \quad (2.23)$$

If  $E_F \gg E_D$ :

$$n_N = N_D \exp\left(\frac{E_F - E_D}{KT}\right) \quad (2.24)$$

forall  $T^\circ$ :

$$n_N = N_C \exp\left(\frac{E_F - E_C}{KT}\right) \quad (2.25)$$

Therefore:

$$n_N = \sqrt{N_C N_D} \exp\left(\frac{E_D - E_C}{2K}\right) \quad (2.26)$$

### Case of a P-type semiconductor

If  $T^\circ < 100K$

$$P_p = \frac{N_A}{1 + \exp\left(\frac{E_A - E_F}{KT}\right)} \quad (2.27)$$

If  $E_A \gg E_F$ :

$$P_p = N_A \exp\left(\frac{E_A - E_F}{KT}\right) \quad (2.28)$$

forall  $T^\circ$ :

$$P_p = N_V \exp\left(\frac{E_V - E_F}{KT}\right) \quad (2.29)$$

So :

$$P_p = \sqrt{N_V N_A} \exp\left(\frac{E_V - E_A}{2KT}\right) \quad (2.30)$$

$(E_D - E_C)$  and represent the ionization energies of the donors and acceptors respectively.  $(E_V - E_A)$

### b. Medium temperature region: $100K < T^\circ < 400K$

For intermediate temperatures all impurities are ionized.

### Case of an N-type semiconductor

In this case all the donors are ionized, we have:  $n_N = N_D$  and  $n_N \cdot p_N = n_i^2$

$$p_N = \frac{n_i^2}{N_D} \quad (2.31)$$

### Case of a P-type semiconductor

In this case all the acceptors are ionized, we write:  $p_P = N_A$ ,  $n_P \cdot p_P = n_i^2$

$$\rightarrow n_P = \frac{n_i^2}{N_A} \quad (2.32)$$

### c. High temperature region $T > 400\text{K}$

In this temperature range the extrinsic semiconductor behaves like an intrinsic semiconductor, therefore: and  $n_p = p_p = n_i$  and  $n_N = p_N = n_i$

## 2.4. Determination of the Fermi level

It is very important to know the position of the Fermi level  $E_F$  since it determines the concentrations of free carriers. Also, knowing its position allows us to know the electronic transport properties (conductivity, etc.) in semiconductors. To determine the position and energy  $E_F$  of the Fermi level, taking the case of an extrinsic semiconductor with  $N_D$  donor and  $N_A$  acceptors. will be deduced after solving the neutrality equation

$$n + N_A^- = p + N_D^+$$

(2.33)

With  $n$  and  $p$ , being the respective concentrations of electrons and holes. And  $N_D^+$ ,  $N_A^-$  represent the concentrations of the ionized donor and acceptor dopants respectively.

$$\begin{cases} N_D = N_D^+ + N_D^0 \\ N_A = N_A^- + N_A^0 \end{cases} \quad (2.34)$$

$N_D$  et  $N_A$  are the total concentrations of donors and acceptors respectively.  $N_D^0$  and  $N_A^0$  are the concentrations of non-ionized donors and acceptors respectively.

$$N_D = \frac{N_D^+}{1 + \exp\left(\frac{E_F - E_D}{kT}\right)} \quad (2.35)$$

$$N_A = \frac{N_A^-}{1 + \exp\left(\frac{E_A - E_F}{kT}\right)} \quad (2.36)$$

### 2.4.1. Approximate method

#### a. Low temperature region

- Case of an N-type semiconductor

$$n = N_C \exp \left( \frac{E_F - E_C}{KT} \right) = N_D \exp \left( \frac{E_D - E_{FN}}{KT} \right) \quad (2.37)$$

$$E_{FN} = \frac{E_C + E_D}{2} + \frac{KT}{2} \ln \frac{N_D}{N_C} \quad (2.38)$$

- P-type semiconductor

$$p = N_V \exp \left( \frac{E_V - E_F}{KT} \right) = N_A \exp \left( \frac{E_{FP} - E_A}{KT} \right) \quad (2.39)$$

$$E_{FP} = \frac{E_V + E_A}{2} - \frac{KT}{2} \ln \frac{N_A}{N_V} \quad (2.40)$$

#### b. Intermediate temperature region

- N-Type Semiconductor

In this case:

$$n = N_C \exp \left( \frac{E_F - E_C}{KT} \right) = N_D \quad (2.41)$$

$$E_{FN} = E_C + KT \ln \frac{N_D}{N_C} \quad (2.42)$$

- P-Type Semiconductor

In this case:

$$p = N_V \exp \left( \frac{E_V - E_F}{KT} \right) = N_A \quad (2.43)$$

$$E_{FP} = E_V - KT \ln \frac{N_A}{N_V} \quad (2.44)$$

### c. High temperature region

In this region, the extrinsic semiconductor (N or P) behaves like an intrinsic semiconductor such that:

$$E_{Fi} = \frac{E_C + E_V}{2} - \frac{KT}{2} \ln \frac{N_C}{N_V}$$

#### 2.4.2. Graphical method

Based on the neutrality equation, the Fermi level can be determined graphically as follows:

$$n + N_A^- = p + N_D^+ \quad (2.45)$$

We entered the natural logarithm on both sides of the equation, we obtain

$$\ln(n + N_A^-) = \ln(p + N_D^+) \quad (2.46)$$

##### a. Let's draw first $\ln(n)$

We have:  $n = N_C \exp\left(\frac{E_F - E_C}{KT}\right) \quad (2.47)$

$$\ln(n) = \ln(N_C) + \frac{E_F - E_C}{KT} \quad (2.48)$$

If  $E_F = E_C \quad >>>>> \quad \ln(n) = \ln(N_C)$

If  $>>>>> E_F = E_V \quad \ln(n) = \ln(N_C) + \frac{E_V - E_C}{KT} = \ln(N_C) - \frac{E_g}{KT} \quad (2.49)$

##### b. Let's draw $\ln(p)$

$$p = N_V \exp\left(\frac{E_V - E_F}{KT}\right) \quad (2.50)$$

$$\ln(p) = \ln(N_V) + \frac{E_V - E_F}{KT} \quad (2.51)$$

If  $E_F = E_V \quad >>>> \quad \ln(p) = \ln(N_V)$

If  $E_F = E_C \quad >>>>> \quad \ln(p) = \ln(N_V) + \frac{E_V - E_C}{KT} = \ln(N_V) - \frac{E_g}{KT} \quad (2.52)$

c. Let's draw  $\ln(N_D^+)$  et  $\ln(N_A^-)$ For  $N_D^+$ :

$$N_D^+ = \frac{N_D}{1 + \exp\left(\frac{E_F - E_D}{KT}\right)} \quad (2.53)$$

If  $E_F > E_D$       >>>>>>       $\ln(N_D^+) = \ln(N_D) + \frac{E_D - E_F}{KT}$       (2.54)

- If  $E_F = E_D$       >>>>>>>       $\ln(N_D^+) = \ln(N_D)$       (2.55)

- If  $E_F = E_C$       >>>>>>>       $\ln(N_D^+) = \ln(N_D) + \frac{E_D - E_C}{KT}$       (2.56)

- If  $E_F < E_D$       >>>>>>>       $\ln(N_D^+) = \ln(N_D)$       (2.57)

For  $N_A^-$ :

$$N_A^- = \frac{N_A}{1 + \exp\left(\frac{E_A - E_F}{KT}\right)} \quad (2.58)$$

If  $E_F > E_A$       >>>>>>       $\ln(N_A^-) = \ln(N_A) + \frac{E_F - E_A}{KT}$       (2.59)

- If  $E_F = E_A$       >>>>>>>       $\ln(N_A^-) = \ln(N_A)$       (2.60)

- If  $E_F = E_V$       >>>>>>>       $\ln(N_A^-) = \ln(N_A) + \frac{E_V - E_A}{KT}$       (2.61)

- If  $E_F < E_A$       >>>>>>>       $\ln(N_A^-) = \ln(N_A)$       (2.62)

Approximation:

To plot  $\ln(n + N_A^-)$  we make the following approximation:

If  $n > N_A^-$       >>>>>>       $\ln(n + N_A^-) = \ln(n)$       (2.63)

If  $n < N_A^-$       >>>>>>       $\ln(n + N_A^-) \approx \ln(n)$       (2.64)

To plot  $\ln(p + N_D^+)$  we make the following approximation:

If  $p > N_D^+$       >>>>>>       $\ln(p + N_D^+) = \ln(p)$       (2.65)

If  $p < N_D^+$       >>>>>>       $\ln(p + N_D^+) \approx \ln(p)$       (2.66)

We determine graphically  $\ln(n + N_A^-)$  and  $\ln(p + N_D^+)$  as a function of  $E_F$ , the intersection of the two curves determines the position of at a given temperature.

By simply reading the graph we can deduce  $E_F$ ,  $n$ ,  $N_A^-$ ;  $p$  and  $N_D^+$

**Note:** In all calculations the temperature is fixed.

## 2.5. Electronic transport principle

### 2.5.1 Study of charge transport mechanisms

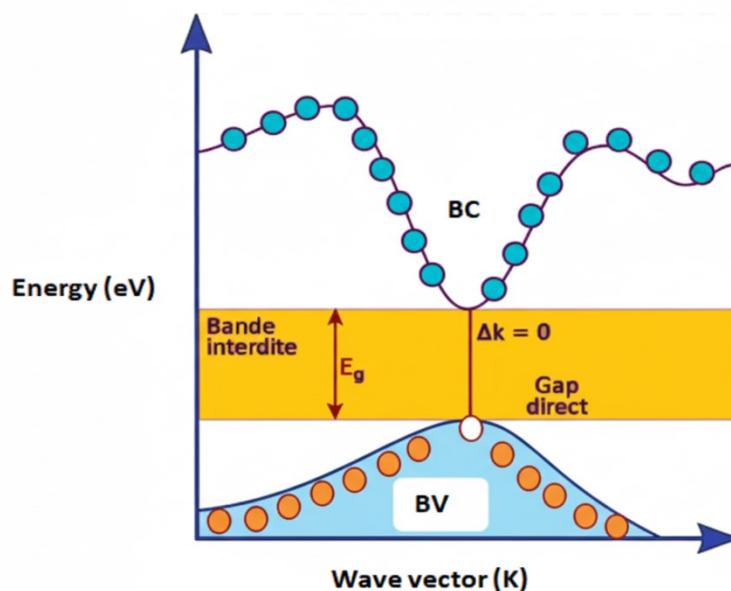

For an intrinsic semiconductor  $n=p=n_i$ . When the crystal is not subjected to any external excitation, it is in equilibrium. At 0°C, all electrons are in the valence band. In this case, the semiconductor behaves like an insulator (the charges are immobile). Under the effect of a temperature gradient, energy is transmitted to the crystal; certain electrons can pass from the valence band (BV) to the conduction band (BC), crossing the band gap (BG). To be able to carry out this movement, the electrons must have an energy  $\geq$  the gap  $E_g$ . The released electrons acquire certain energy; translated by a thermal velocity  $v$ . The electrons follow random paths with the atoms in the lattice.

**Figure 2.3:** Representation of a direct bandgap semiconductor

The momentum of the electrons is then:  $m_n^* v = \hbar k$  (2.67)

With: the effective mass of the electrons and the wave vector.  $m_n^* k$  (2.68)

The average speed of electrons is calculated by:  $\frac{1}{2} m_n^* \bar{v}^2 = \frac{3}{2} kT$  (2.69)

K: Boltzmann constant,  $\bar{v}$ : average speed

The mean free path can be defined as the average distance traveled between two collisions, to which we associate an average time called such that:  $\bar{l}\tau\bar{l} = \tau \cdot \bar{\vartheta}$

### 2.5.2 Applying an electric field to the crystal

#### a. Mobility of electrons and holes

By applying an electric field  $\vec{E}$  to the crystal, the electrons are subjected to an electric force  $\vec{F}$  given by:

$$\vec{F} = m_n^* \cdot \frac{d\vec{v}_n}{dt} = -q\vec{E} \quad (2.70)$$

$$\text{If at } t=0, v_n = v_0 \gg \gg \gg \gg \gg \frac{dv_n}{dt} = -\frac{qE}{m_n^*} \gg \gg \gg \gg \gg v_n - v_0 = -\frac{qEt}{m_n^*} \quad (2.71)$$

If at  $t = \tau$ ,  $v_n = \bar{\vartheta} \gg \gg \gg \gg \gg \bar{\vartheta} - v_0 = -\frac{q\tau}{m_n^*} E = \mu_n E$  or  $\mu_n$  represents the mobility of the electrons:

$$|\mu_n| = \frac{V}{E} = \frac{q\tau}{m_n^*} \left( \frac{cm^2}{V.s} \right) \quad (2.72)$$

A similar reasoning allows us to define the mobility of holes

$$|\mu_p| = \frac{V}{E} = \frac{q\tau}{m_p^*} \left( \frac{cm^2}{V.s} \right) \quad (2.73)$$

**Noticed:** Generally  $\mu_n \approx 3\mu_p$

#### b. Electrical conductivity

Let  $\rho_n$  and  $\rho_p$  be the volume densities of charges of electrons and holes respectively.

The densities of conduction currents are respectively:  $\rho_n \rho_p$

$$\vec{J}_n^c = \rho_n \bar{\vartheta}_n^c \vec{J}_p^c = \rho_p \bar{\vartheta}_p^c \quad (2.74)$$

$$\bar{\vartheta}_n^c = -\mu_n \cdot \vec{E}, \bar{\vartheta}_p^c = \mu_p \cdot \vec{E} \quad (2.75)$$

$$\vec{J}_n^c = -\rho_n \mu_n \cdot \vec{E} \vec{J}_p^c = \rho_p \mu_p \cdot \vec{E} \quad (2.76)$$

with  $\rho_n = -qn$  and  $\rho_p = qp$ ,  $\vec{J}_n^c = qn\mu_n \cdot \vec{E}$  and  $\vec{J}_p^c = qp\mu_p \cdot \vec{E}$

Subsequently  $\vec{J}_n^c = \sigma_n \cdot \vec{E}$  and  $\vec{J}_p^c = \sigma_p \cdot \vec{E}$

$\sigma_n = qn\mu_n$  and  $\sigma_p = qn\mu_p$  are respectively the electrical conductivities of electrons and holes expressed in  $\Omega^{-1}\text{cm}^{-1}$

The total current density is therefore:

$$\vec{J}_{tot}^c = \vec{J}_n^c + \vec{J}_p^c = q(n\mu_n + p\mu_p)\vec{E} \quad (2.77)$$

Where  $\sigma_{tot} = q(n\mu_n + p\mu_p)$

If the semiconductor is intrinsic  $n = p = n_i$

→  $\sigma_{tot} = qn_i(\mu_n + \mu_p)$  and  $\rho_{tot} = \frac{1}{\sigma_{tot}} = \frac{1}{(qn_i(\mu_n + \mu_p))}$

If the semiconductor is N-type, the concentration of electrons increases.

At 300K  $\Rightarrow n = N_D \vec{J}_{tot}^c = \vec{J}_n^c = qN_D \mu_n \vec{E}$  (2.78)

If the semiconductor is P-type, the concentration of holes increases.

At 300K.  $\Rightarrow p = N_A \vec{J}_{tot}^c = \vec{J}_p^c = qN_A \mu_p \vec{E}$  (2.79)

### 2.5.3 Diffusion and continuity equations of minority carriers

#### a. Diffusion of minority interests

In a semiconductor, the movement of free carriers is due either to entrainment under the effect of an applied electric field, or to diffusion when there is a concentration gradient. When the semiconductor is subjected to light excitation, i.e. photonic energy ( $E = h\nu = \frac{hc}{\lambda}$ ), excess charge carriers are created in the illuminated region compared to the equilibrium concentrations  $\bar{n}$  and  $\bar{p}$ . We therefore have a non-equilibrium phenomenon due to the increase in concentrations  $n$  and  $p$

For an N-type semiconductor at equilibrium  $\bar{n} = N_D$ , and if the semiconductor is P-type.  $\bar{p} = N_A$

We will study the diffusion of minority carriers in the case of a P-type semiconductor ( $\bar{p} > \bar{n}$ ).

Note that diffusion only concerns minority carriers, which in this case are electrons. These are more numerous in the illuminated medium and move towards the low concentration region.

**Minority carriers move from the region of higher concentration to the region of lower concentration in order to achieve a uniform charge balance**

The medium after excitation must become electrically neutral. The electrons will recombine with the holes and it is only at a certain distance from the illuminated region that the equilibrium concentration is found. We say that diffusion of minority carriers occurs each time there is a concentration gradient and it tends to flow in the direction of decreasing concentrations.  $\bar{n}$ .

The flow of electrons is expressed by:  $F_n = -D_n \overrightarrow{grad}n = -\frac{dn}{dx}$  (2.80)

In the case of an N-type semiconductor:  $F_p = -D_p \overrightarrow{grad}P = -\frac{dp}{dx}$  (2.81)

$D_n$  et  $D_p$  are the diffusion constants of electrons and holes respectively

We deduce the diffusion currents:

**For electrons:**  $\overrightarrow{J_n^D} = -q\vec{F}_n = qD_n \overrightarrow{grad}n = qD_n \frac{dn}{dx}$  (2.82)

**For the holes:**  $\overrightarrow{J_p^D} = -q\vec{F}_p = qD_p \overrightarrow{grad}P = qD_p \frac{dp}{dx}$  (2.83)

A semiconductor contains both types of charge carriers. These carriers move under the effect of:

- An electric field: we therefore have a conduction current

- A concentration gradient: we therefore have a conduction current

In the case of a semiconductor where the concentration of carriers is not uniform and to which an electric field is applied, we will therefore have the sum of the two diffusion and conduction currents:  $J_{tot} = J^c + J^D$

So:

$$J_n = J_n^D + J_n^C = qD_n \overrightarrow{grad}n + qn\mu_n \cdot \vec{E} \quad (2.84)$$

$$J_p = J_p^D + J_p^C = qD_p \overrightarrow{grad}P + qp\mu_p \cdot \vec{E} \quad (2.85)$$

**Noticed:** At thermodynamic equilibrium the total current densities are zero

### b. Einstein's relationships

They are expressed as follows:

$$\frac{D_n}{\mu_n} = \frac{D_p}{\mu_p} = \frac{KT}{q} \quad (2.86)$$

### c. Non-equilibrium semiconductor (injection and extraction of charge carriers)

Most electronic devices operate outside of equilibrium conditions. At thermodynamic equilibrium:  $\bar{n} \cdot \bar{p} = n_i^2$

In the non-equilibrium case  $n \cdot p \neq n_i^2$ , where  $n$  and  $p$  are the non-equilibrium concentrations of electrons and holes.

If  $n \cdot p > n_i^2$ : we are talking about carrier injection

If  $n \cdot p < n_i^2$ : we are talking about carrier extraction

$$\begin{cases} n = \bar{n} + D_n = n + \hat{n} \\ p = \bar{p} + D_p = p + \hat{p} \end{cases} \quad (2.87)$$

$\hat{n}$  et  $\hat{p}$  : are the concentrations of excess electrons and holes.

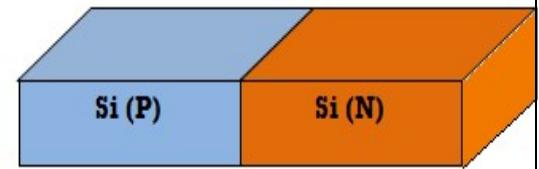

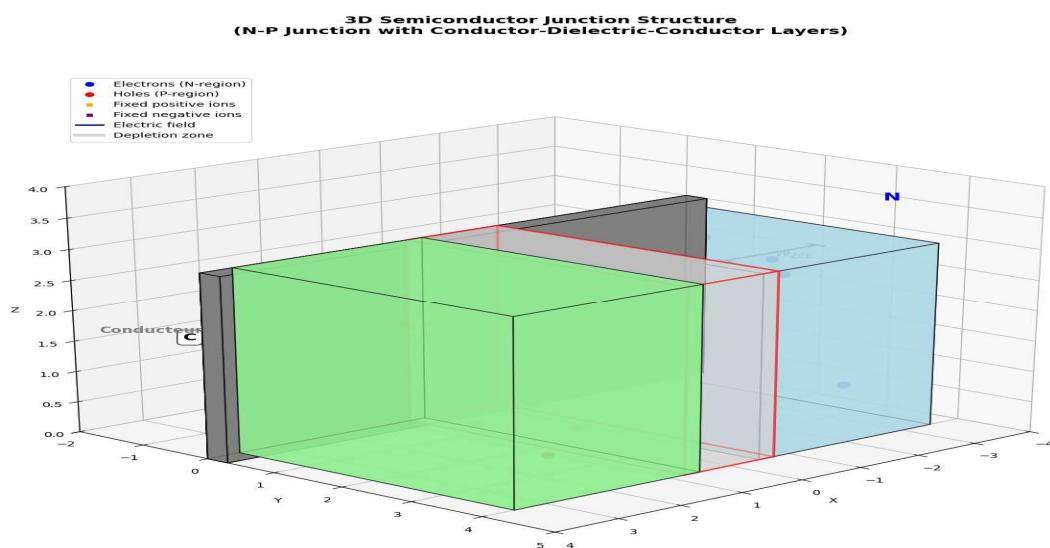

## Chapter III: PN Junction physic

### Introduction

The PN junction plays an important role in current electronics. It is involved in the production of many electronic devices and circuits, including diodes, bipolar transistors, JFET field-effect transistors, and solar cells. The PN junction is obtained by juxtaposing two differently doped P and N semiconductors. It is not just a simple juxtaposition of two semiconductors; the contact between the two semiconductors must be a continuity of the crystal lattice on either side of the junction surface.

There are two types of junctions:

a. **Homojunction**: we speak of Homojunction when the junction is obtained from a single semiconductor bar such as silicon or germanium.

b. **Heterojunction**: the heterojunction is made from two different semiconductors

If the semiconductor type is replaced by a conductor (metal) the junction is called: Schottky junction

The doping of both N and P regions is done either by the diffusion process or by ion implantation (for more details on these two processes, see the course "**integrated circuit manufacturing technology**").

Depending on the evolution of the concentration of dopants, two types of homojunction are distinguished:

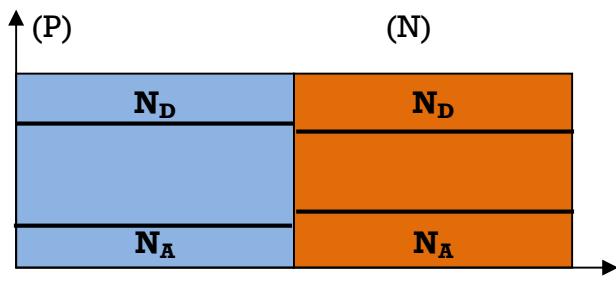

**Abrupt homojunction:**

The junction is said to be abrupt when the  $N_A$  and  $N_D$  concentrations are constant across the semiconductor rod. Otherwise, an abrupt junction is by definition a junction in which the doping type changes over a very small distance compared to the spatial extent of the depletion region.

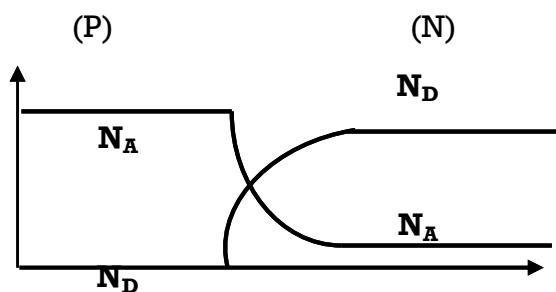

**Gradual homojunction:**

In this type of junction the  $N_A$  and  $N_D$  concentrations vary gradually.

In this chapter, a simplified one-dimensional (1D) qualitative study of the properties of a Homojunction will be presented.

**Figure 3.1:** Abrupt homojunction

**Figure 3.2:** Gradual homojunction

### 3.1 Qualitative study of the operation of a junction

We place ourselves at an ordinary temperature of 300K without any external disturbance. We create an abrupt junction by gradually bringing together two crystals with different doping. Before physical contact between the two regions, there is equilibrium and all the dopants are ionized.

---

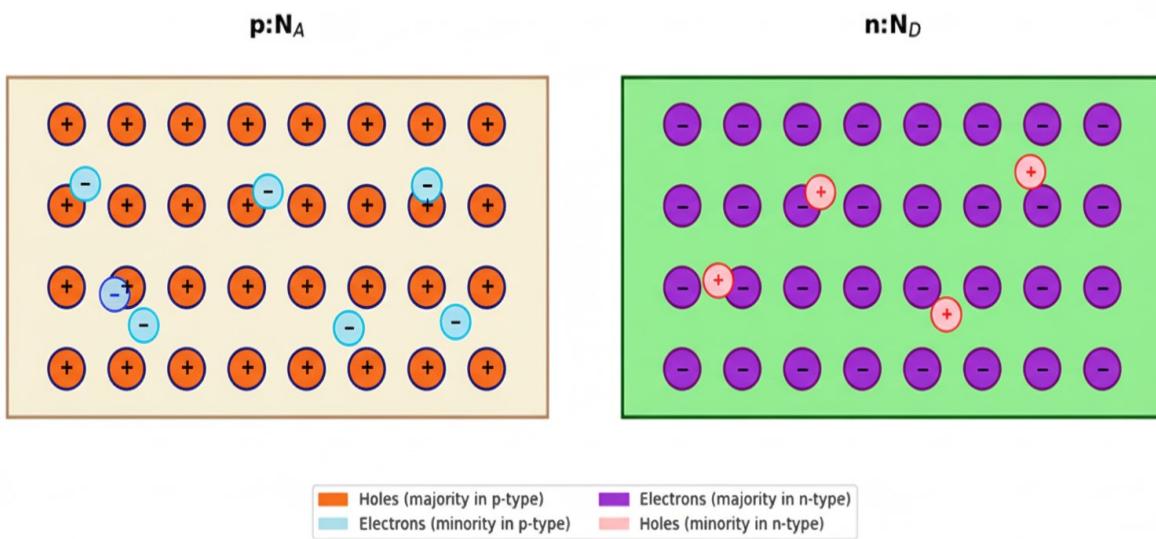

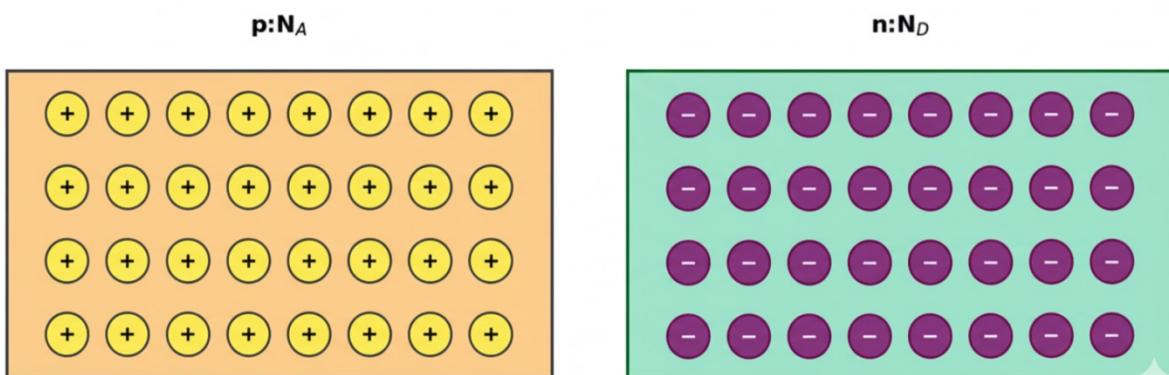

### P-N Junction: Charge Carrier Distribution

---

### P-N Junction: Simplified Carrier Distribution

**Figure 3.3:** P-N Junction diagram with charge carriers

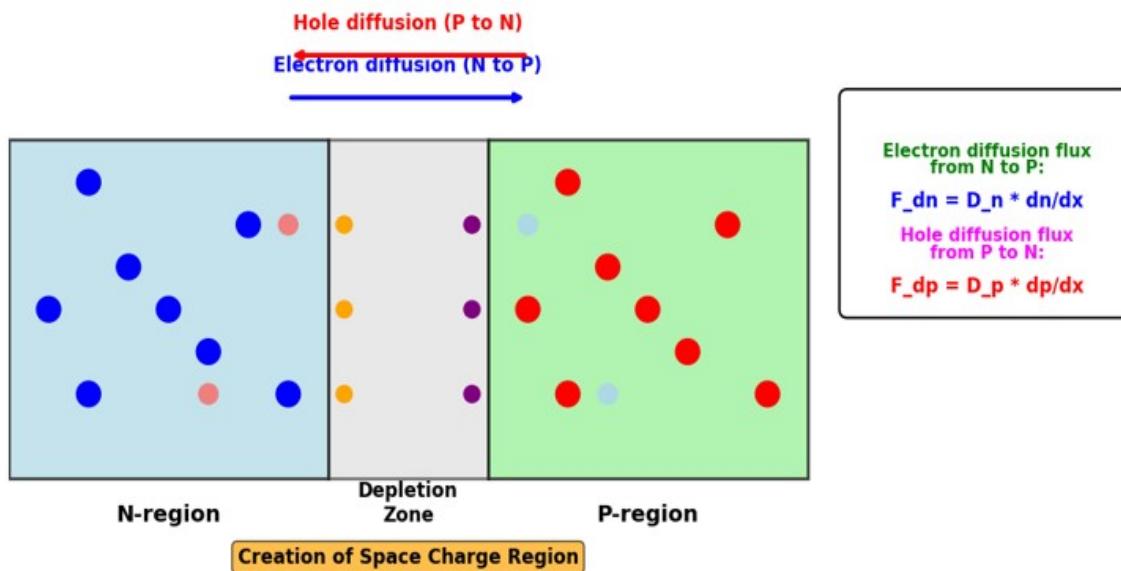

When contact is established, a concentration gradient appears on either side of the contact surface. The carriers diffuse from the more doped side to the less doped side (see figure below). We therefore have:

- An electron flow towards the P region

- A flow of holes to the N region

## Simultaneous Diffusion in Semiconductor Junction

Figure 3.4: Simultaneous diffusion in PN Junction

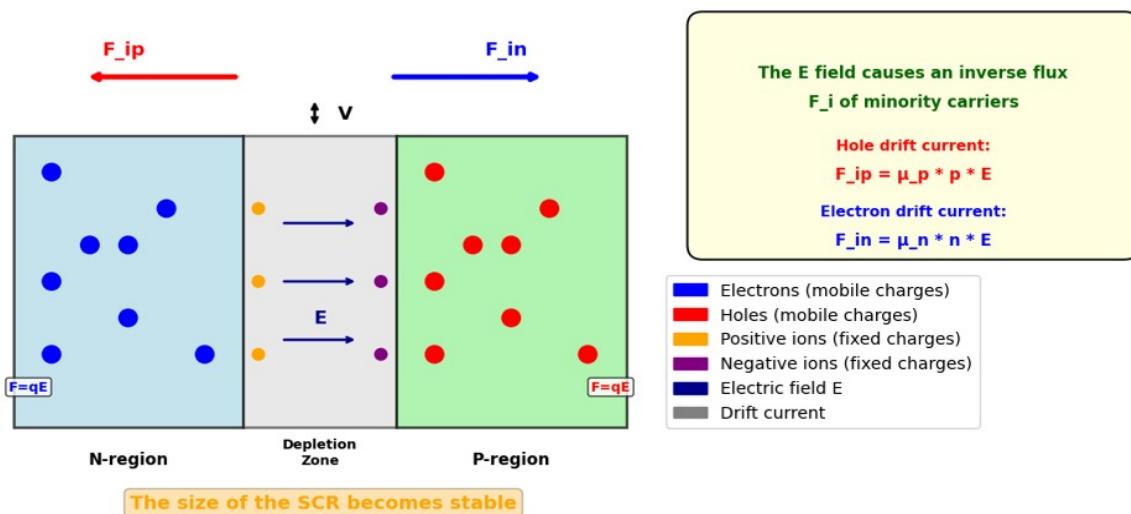

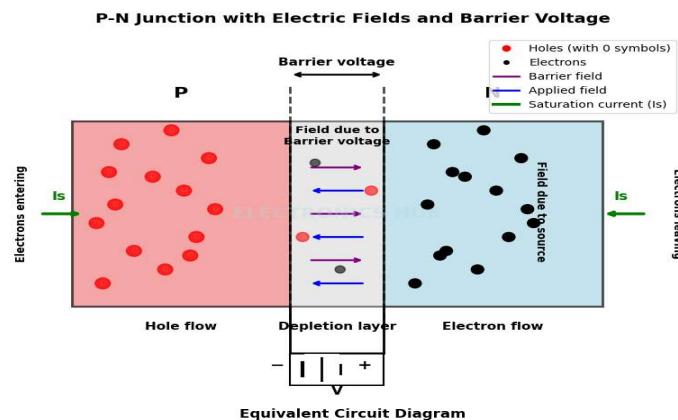

When equilibrium is established, a depleted area (depletion region) of charges is formed. This area is called the space charge zone SCZ. In this area, an internal electric field called “diffusion field” is produced. It is directed from the N side (positively charged) to the P side (negatively charged).

## Electric Field and Drift Currents in Semiconductor Junction

Figure 3.5: Representation of the internal electric field in the SCZ.

When the diffusion field becomes strong enough it opposes the diffusion phenomenon of the majority until thermodynamic equilibrium has occurred and diffusion is composed by conduction ( $J_N=J_P=0$ ). Moreover, at thermodynamic equilibrium, diffusion and internal fluxes become equal i.e.,  $F_{in}=F_{dn}$  (**N side**) and  $F_{ip}=F_{dp}$  (**P side**). In this case the Fermi level remains constant throughout the structure.

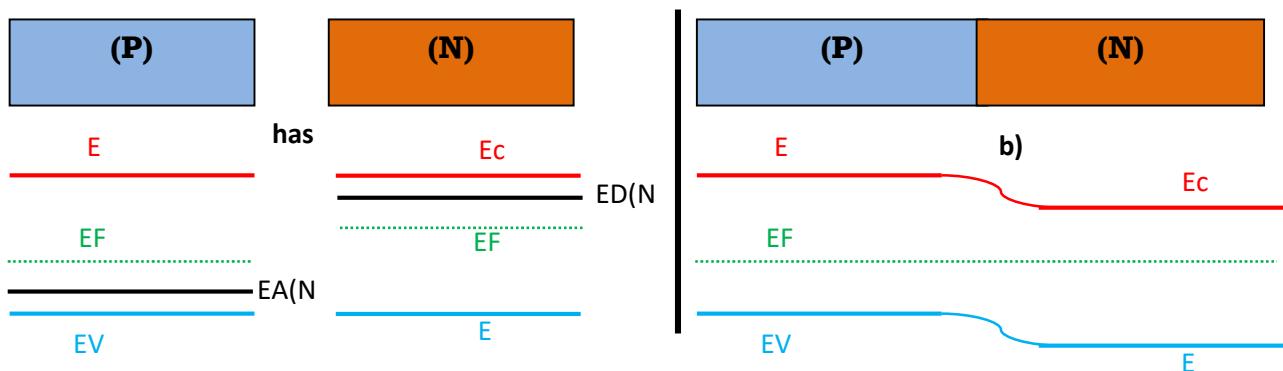

**Figure 3.6:** Representation of the Fermi level:

**Left)** Before junction contact; **Right)** After contact.

### 3.2 Study of the abrupt PN junction

#### 3.2.1. Charges distribution

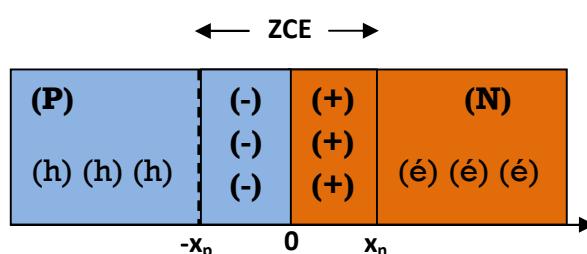

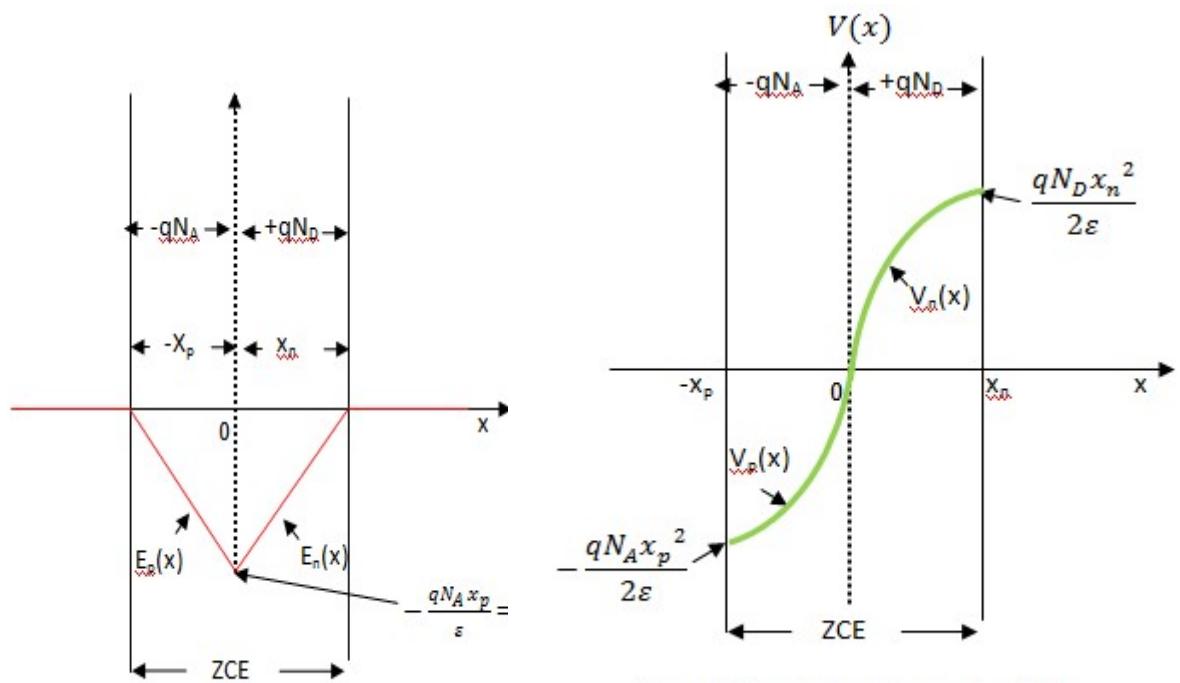

The equation that describes the charge density  $\rho(x)$  across the depletion region is given by:

$$\rho(x) = \begin{cases} +qN_D & \text{si } 0 < x < x_n \\ -qN_A & \text{si } -x_p < x < 0 \\ 0 & \text{ailleurs} \end{cases} \quad (3.1)$$

So, the charge is not uniform; it's a dipole layer of fixed opposite charges on either side of the junction.

### 3.2.2. Variation of the electric field

To determine the spatial distribution of the electric field across the junction we used Poisson's equation:

$$\operatorname{div} E = \frac{\rho(x)}{\varepsilon} \gggggggggg \frac{dE}{dx} = \frac{\rho(x)}{\varepsilon} \quad (3.2)$$

With:  $\varepsilon = \varepsilon_0 + \varepsilon_r$

If  $0 < x < x_n$ :

$$\frac{dE}{dx} = \frac{+qN_D}{\varepsilon} \gggggg E_n(x) = \int \frac{+qN_D}{\varepsilon} dx \quad (3.3)$$

$$E_n(x) = \frac{+qN_D}{\varepsilon} x + cst1 \quad (3.4)$$

To determine the constant  $cst1$  we use the boundary condition:

$$x = x_n \gggggg E_n(x_n) = 0 \gggggg cst1 = \frac{-qN_D x_n}{\varepsilon} \quad (3.5)$$

So:

$$E_n(x) = \frac{qN_D}{\varepsilon} x - \frac{qN_D}{\varepsilon} x_n = \frac{qN_D}{\varepsilon} (x - x_n) \quad (3.6)$$

If  $-x_p < x < 0$ :

$$\frac{dE}{dx} = \frac{-qN_A}{\varepsilon} \gggggg E_p(x) - \int \frac{qN_A}{\varepsilon} dx \quad (3.7)$$

$$E_p(x) = \frac{-qN_A}{\varepsilon} x + cst2 \quad (3.8)$$

In the same way we determine the  $cst2$ :

$$x = -x_p \gggggg E_p(-x_p) = 0 \gggggg cst1 = -\frac{qN_A x_p}{\varepsilon} \quad (3.9)$$

So:

$$E_p(x) = -\frac{qN_A}{\varepsilon} x + \frac{qN_A}{\varepsilon} x_p = -\frac{qN_A}{\varepsilon} (x + x_p) \quad (3.10)$$

According to the condition of continuity of the electric field  $E_n(x = 0) = E_p(x = 0)$ :

$$x_n N_D = x_p N_A$$

From this last equation we conclude that the SCZ extends on the weakly doped side.

**Figure 3.7:** Distribution across the depletion region of: **Left:** Electric field, **Right:** Electrostatic potential

### 3.2.3. Distribution of electrostatic potential

If  $0 < x < x_n$  :

$$E = -\text{grad } V \implies V = - \int E dx \quad (3.11)$$

$$V_n(x) = -\frac{qN_D}{\epsilon} \int (x - x_n) dx \quad (3.12)$$

$$V_n(x) = -\frac{qN_D}{2\epsilon} (x^2 - 2xx_n) + cst1 \quad (3.13)$$

If  $-x_p < x < 0$  :

$$V_p(x) = \frac{qN_A}{\epsilon} (x^2 + xx_p) + cst2 \quad (3.14)$$

We admit that there is continuity in  $x = 0$ ,

$$V_n(x = 0) = V_p(x = 0) = 0 \implies cst1 = cst2 = 0 \quad (3.15)$$

So:

$$V_n(x) = -\frac{qN_D}{2\epsilon} (x^2 - 2xx_n) \quad (3.16)$$

$$V_p(x) = \frac{qN_A}{2\varepsilon} (x^2 + 2xx_p) \quad (3.17)$$

### 3.2.4. Diffusion voltage

The potential difference in the PN junction is expressed by:  $V_D$

$$V_D = V_n(x_n) - V_p(-x_p) = \frac{q}{2\varepsilon} (N_D x_n^2 + N_A x_p^2) \quad (3.18)$$

We deduce:

$$V_D = \frac{KT}{q} \ln\left(\frac{N_A N_D}{n_i^2}\right) \quad (3.19)$$

$$n_i^2 = N_C N_V \exp\left(\frac{-E_g}{KT}\right) \quad (3.20)$$

### 3.2.5. Calculation of the width of the SCZ: $W_{SCZ}$

$$x_n = \sqrt{\frac{2\varepsilon V_D N_A}{q N_D (N_A + N_D)}} \quad (3.21)$$

$$x_p = \sqrt{\frac{2\varepsilon V_D N_D}{q N_A (N_A + N_D)}} \quad (3.22)$$

$$W_{SCZ} = x_n + x_p = \sqrt{\frac{2\varepsilon V_D}{q} \frac{N_A + N_D}{(N_A N_D)}} \quad (3.23)$$

### 3.2.6. Diffusion capacity: $C_d$

We assume that SCZ is a thick insulator surrounded by two slightly conductive regions. So we have the structure of a planar capacitor. Its capacitance is called diffusion capacitance and is noted  $C_d$  as follows:

$$C_d = \frac{\varepsilon S}{W_{SCZ}} = S \sqrt{\frac{q\varepsilon}{2} \frac{N_A N_D}{V_D (N_A + N_D)}} \quad (3.24)$$

**Figure 3.8:** Illustration of the junction capacity

### 3.3 Polarization of the PN junction

We speak of a polarized junction when its terminals are connected to an external voltage generator  $V$ . Its aim is to create an electric field to drain the electrons in order to generate an electric current in the junction. By convention, the current of the junction is positive when it flows from the P region to the N region. Two modes of polarization are distinguished:

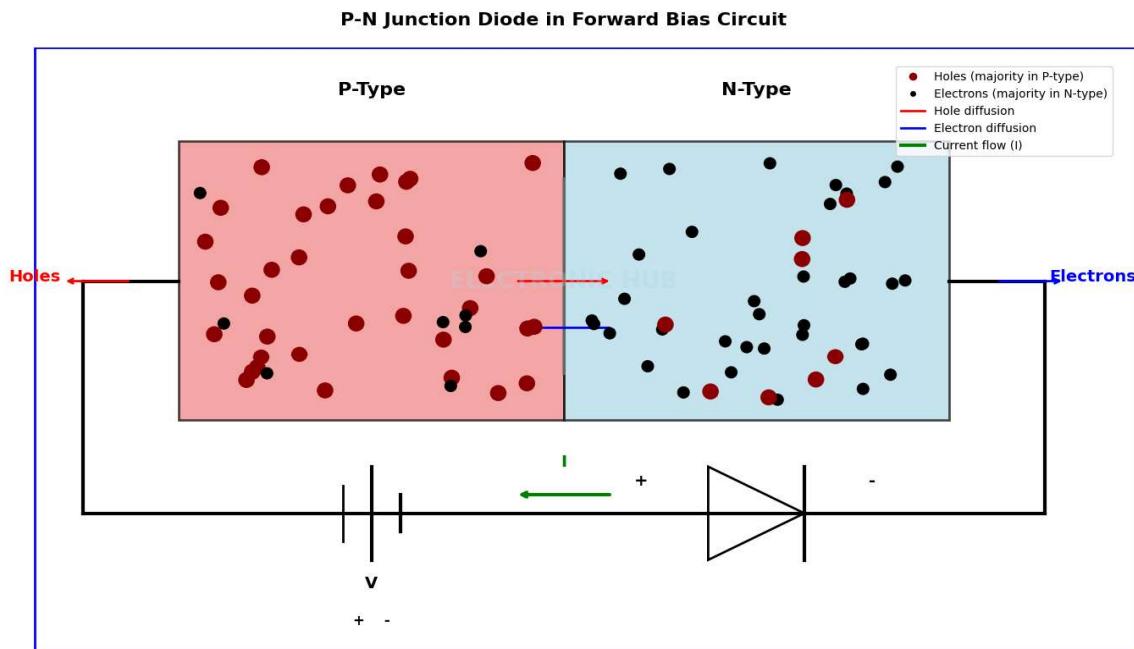

#### 3.3.1 Forward polarization

The voltage across the junction will therefore be:  $U = V_D - V$ . Subsequently, the width of the depletion region, as well as the diffusion capacity become respectively:

$$W_{ZCE} = x_n + x_p = \sqrt{\frac{2\epsilon(V_D - V)}{q} \frac{N_A N_D}{(N_A + N_D)}} \quad (3.25)$$

$$C_d = \frac{\epsilon S}{W_{ZCE}} = S \sqrt{\frac{q\epsilon}{2(V_D - V)} \frac{N_A N_D}{(N_A + N_D)}} \quad (3.26)$$

**Figure 3.9:** Forward biased PN junction

### 3.3.2 Reverse bias

In this case the voltage across the junction will therefore be:  $U = V_D + V$ . In this case, the width of the depletion region, as well as the diffusion capacity are expressed as follow:

$$W_{ZCE} = x_n + x_p = \sqrt{\frac{2\varepsilon(V_D + V)}{q} \frac{N_A + N_D}{(N_A N_D)}} \quad (3.27)$$

$$C_d = \frac{\varepsilon S}{W_{ZCE}} = S \sqrt{\frac{q\varepsilon}{2(V_D + V)} \frac{N_A N_D}{(N_A + N_D)}} \quad (3.28)$$

**Figure 3.10:** Reverse biased PN junction

### 3.4 Concentration of charge carriers within the boundaries of the PN junction

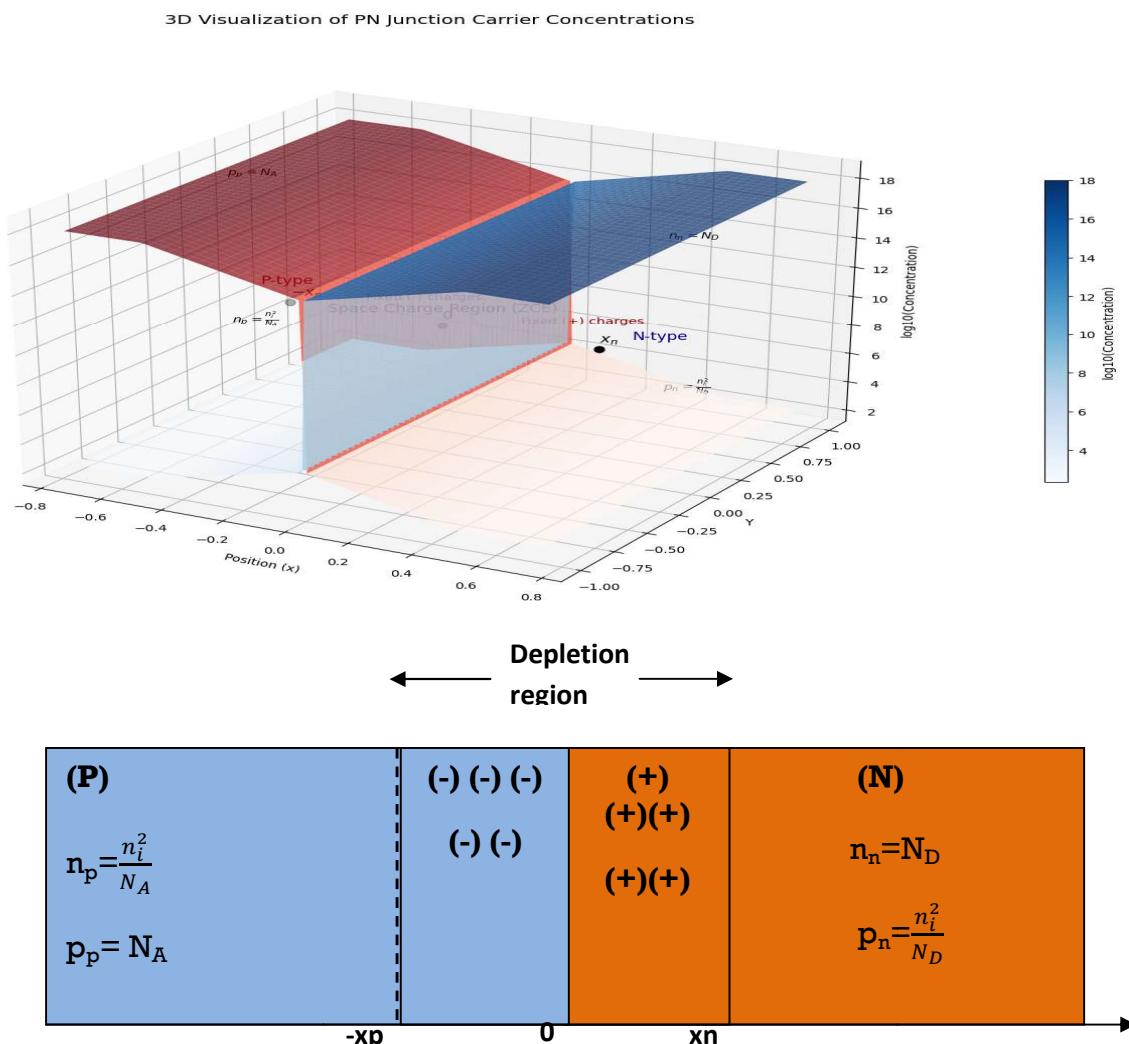

Based on the equation:  $np = n_i^2$ , the distribution of charge carriers, majority and minority, across the junction is given in the figure 3.11.

In balance:

$$P_p = \overline{P_p} = N_A \quad \text{and} \quad n_n = \overline{n_n} = N_D$$

$$n_p = \overline{n_p} e^{\frac{qv}{KT}} \quad \text{and} \quad P_n = \overline{P_n} e^{\frac{qv}{KT}}$$

**Figure 3.11:** Visualization of PN junction carrier's concentration

### 3.5 Spatial distribution of currents at the junction

The current across a p–n junction originates from the diffusion of minority carriers injected into the quasi-neutral regions under bias. Holes from the p-side diffuse into the n-side, while electrons from the n-side diffuse into the p-side. These contributions can be described mathematically as position-dependent diffusion currents, expressed in terms of carrier diffusion lengths, equilibrium minority concentrations, and the applied voltage.

$$I_p(x) = -\frac{qSD_p}{L_p} \overline{p_n} [exp \frac{qv}{kT} - 1] exp \frac{x_n - x}{L_p} \quad (3.29)$$

$$I_n(x) = -\frac{qSD_n}{L_n} \overline{n_p} [\exp \frac{qv}{KT} - 1] \exp \frac{x_p+x}{L_n} \quad (3.30)$$

$$I(x) = qS \left[ \frac{D_n}{L_n} \overline{n_p} + \frac{D_p}{L_p} \overline{p_n} \right] (\exp \frac{qv}{KT} - 1) = I_s (\exp \frac{qv}{KT} - 1) \quad (3.31)$$

With:  $S$  represents the surface of the junction,  $D_n$  and  $D_p$  are respectively the diffusion constants of electrons and holes.  $L_n$ ;  $L_p$  are respectively the diffusion lengths of electrons and holes.  $I_s$  represents the saturation current of the diode and is expressed as follow:

$$I_s = qS \left[ \frac{D_n}{L_n} \overline{n_p} + \frac{D_p}{L_p} \overline{p_n} \right] \quad (3.32)$$

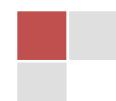

### 3.6 Junction breakdown

By applying a reverse voltage greater than a certain critical value across the junction, the reverse current increases rapidly. This growth can be the result of either Zener breakdown or avalanche breakdown (the phenomenon of rapid splitting of electron-hole pairs).

**Figure 3.12:** Representation of the diode operating zones (PN junction)

## Chapter IV: The bipolar transistor “BJT”

### Introduction

The bipolar transistor is an essential electronic component used in numerous applications, including amplification, switching, and signal processing circuits. This chapter provides a detailed overview of the structure, operation, configurations, characteristics with associated equations and applications.

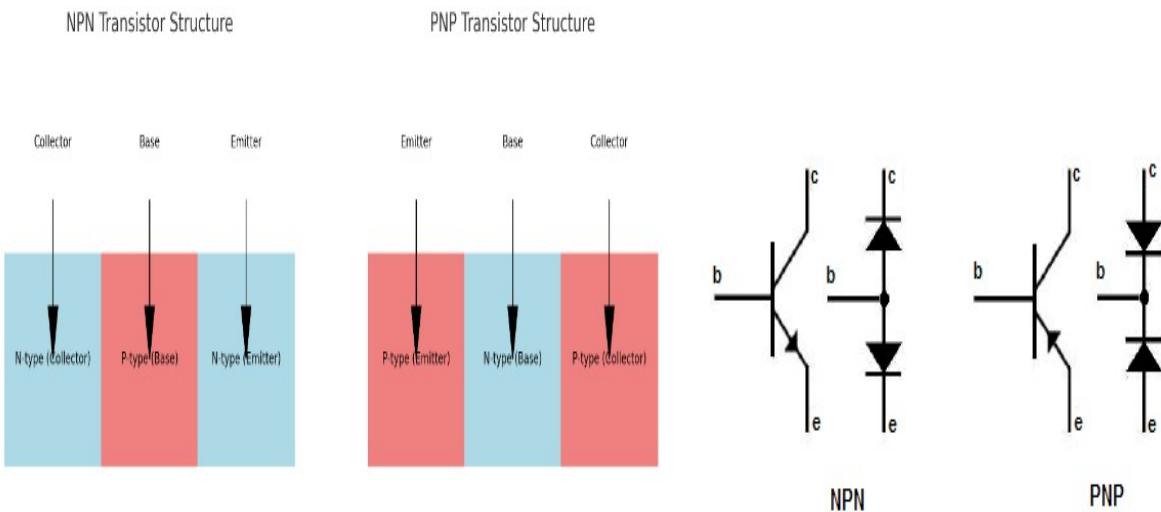

#### 4.1 Structures and Symbols of the Bipolar Transistor

A bipolar transistor consists of three layers of semiconductor material, typically silicon. N-type regions are doped with elements that provide additional electrons, while P-type regions are doped to create 'holes' (absence of electrons). A transistor is made up of three main regions: the emitter, base, and collector.

- **NPN Transistor:** A P-type layer (base) is placed between two N-type layers (emitter and collector).

- **PNP Transistor:** An N-type layer (base) is sandwiched between two P-type layers (emitter and collector).

Below are the basic illustrations of the two types of transistors NPN and PNP structure (left) and their symbols when used as circuit element (right). The arrow on the emitter lead indicates the direction of current flow when the emitter-base junction is forward-biased. For both types of transistors, the currents flowing through the emitter, base, and collector, denoted as  $I_E$ ,  $I_B$ , and  $I_C$ , respectively, are considered positive when flowing into the transistor. The voltages  $V_{BE}$ ,  $V_{CB}$ , and  $V_{CE}$  correspond to the base-emitter, collector-base, and collector-emitter voltages.

**Figure 4.1:** Illustrations of NPN and PNP transistor structures with their symbols

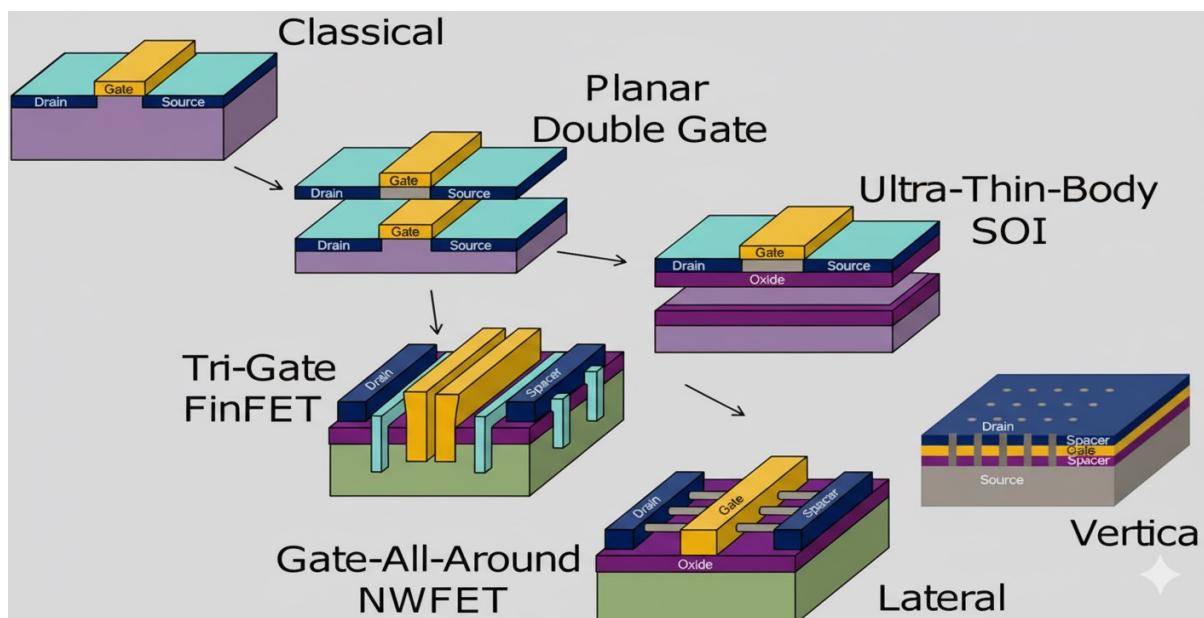

The evolution of semiconductor technology has been marked by groundbreaking advancements that have shaped modern electronics. From the invention of the point-contact transistor in the 1940s to the emergence of two-dimensional materials in recent years, each innovation has contributed to the miniaturization, efficiency, and functionality of electronic devices. The table below summarizes the key methods and technologies in semiconductor development, highlighting their characteristics, applications, and historical significance.

| Era         | Technology/Method                | Key Characteristics                                       | Applications                                                                                                         | References                            |

|-------------|----------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 1940s-1950s | <b>Point-Contact Transistors</b> | Early form of transistors; fragile and low reliability.   | <br>Radios, hearing aids.        | Bardeen & Brattain (1947), Bell Labs. |

| 1950s       | <b>Junction Transistors</b>      | More robust and efficient than point-contact transistors. | <br>Early computers, amplifiers. | Shockley (1951), Bell Labs.           |

|         |                                                                   |                                                                                                           |                                               |                                         |

|---------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------|

| 1960s   | <b>Planar Process (Bipolar Junction Transistors)</b>              | Developed by Jean Hoerni; allowed for mass production and integration.                                    | Integrated Circuits (ICs).                    | Hoerni (1959), Fairchild Semiconductor. |

| 1970s   | <b>MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor)</b> | Enabled high-density integration of transistors on chips.                                                 | Microprocessors, memory chips.                | Kahng & Atalla (1960), RCA Labs.        |

| 1980s   | <b>CMOS (Complementary Metal-Oxide-Semiconductor)</b>             | Low power consumption; dominant technology for digital ICs.                                               | Microcontrollers, mobile devices.             | Mead & Conway (1980), VLSI Revolution.  |

| 1990s   | <b>SOI (Silicon-on-Insulator)</b>                                 | Reduced parasitic effects and power leakage.                                                              | High-speed processors.                        | Tsu-Jae King Liu (1998), UC Berkeley.   |

| 2000s   | <b>High-k/Metal Gate Technologies</b>                             | Improved transistor scaling and reduced leakage currents.                                                 | Advanced microprocessors.                     | Intel & IBM Collaborations (2007).      |

| 2010s   | <b>FinFET (Fin Field-Effect Transistor)</b>                       | 3D structure for higher performance and power efficiency.                                                 | Modern CPUs and GPUs.                         | Hu et al. (2011), Intel.                |

| 2020s   | <b>Gate-All-Around (GAA) Transistors</b>                          | Further miniaturization and power efficiency; successor to FinFET.                                        | AI accelerators, quantum computing.           | Samsung & TSMC (2022).                  |

| Present | <b>2D Materials and Nanotechnology</b>                            | Use of graphene, MoS <sub>2</sub> , and other materials for ultra-small and energy-efficient transistors. | Emerging applications in IoT, AI, and beyond. | Geim & Novoselov (2010), Nobel Prize.   |

**Table. 4.1** The key methods and technologies in semiconductor development

#### 4.2. BJT polarization: how a small signal controls large current flow?

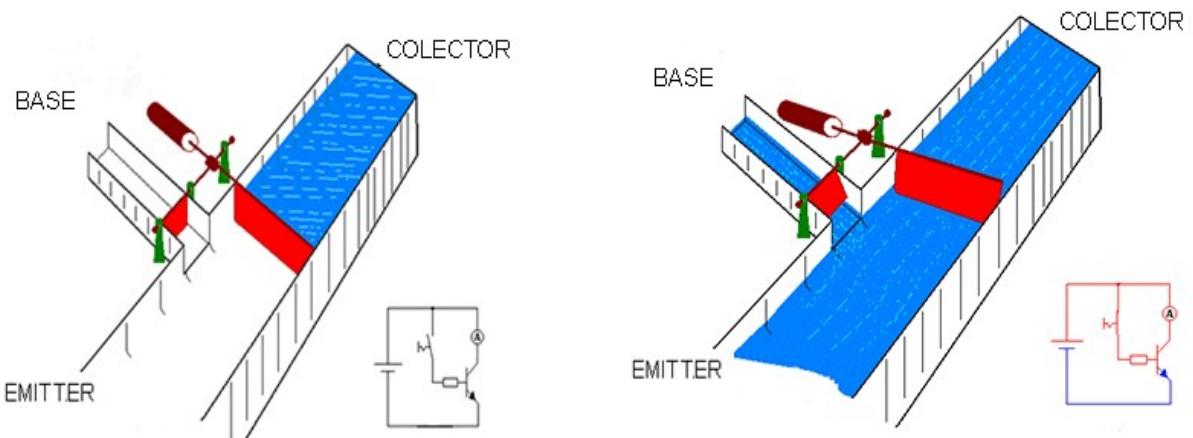

To make a bipolar junction transistor operate correctly, it must be polarized, meaning specific voltages are applied to its terminals to enable current flow. This setup is crucial for the BJT to work as either an amplifier or a switch, and the approach differs slightly for NPN and PNP transistors. The illustration of figure 4.2 shows how a bipolar junction transistor operates using an analogy of water flow to represent the behaviour of electric current in the transistor. This diagram uses a water analogy to explain how a BJT works, showing how a small control action can regulate a larger flow of current. In each illustration, the blue area represents the flow of current through the transistor, while the red paddle or switch connected to the base serves as a control mechanism. Think of it as a small valve that either blocks or allows the flow of water (current) in the main pipe. The pipes represent different regions of the transistor: the emitter, base, and collector.

<https://www.infootec.net/bipolar-transistor-bjt/>

**Figure 4.2:** Understanding bipolar junction transistor operation through a water flow analogy.

According to the left diagram "Off State", the base switch is open. No current flows into the base, which means the flow of water (or current) from the collector to the emitter is blocked. This setup shows the transistor in an "off" state, where it acts as a barrier, preventing any current from flowing through the main circuit.

Essentially, without any input at the base, the transistor prevents the larger current from moving across the collector-emitter path. In the right diagram "On State", the base switch is closed, allowing a small amount of water (current) to flow into the base. This small base current enables a larger current to flow from the collector to the emitter, just as opening a small valve could allow a main water flow to continue downstream. In this "on" state, the transistor allows the main current to pass through the collector and emitter freely, controlled by the small current that's applied at the base.

Under each water analogy is a simplified electrical circuit. It shows the base (B), collector (C), and emitter (E) connections, with a power source attached to the collector and a ground connected to the emitter. In both diagrams, the switch in the base circuit illustrates that a small base voltage (when the switch is closed) controls the larger collector-emitter current.

#### 4.2.1 Polarizing an NPN transistor

- **Base-emitter junction:** This junction needs to be forward-biased. To do this, a small positive voltage is applied to the base relative to the emitter. This setup allows electrons to move from the emitter (an N-type region) toward the base (a P-type region).

- **collector-base junction:** Here, the goal is to reverse-bias the junction, which means applying a larger positive voltage to the collector relative to the base. This reverse bias encourages electrons to travel from the base to the collector, facilitating a flow of current from collector to emitter.

**In action:** When an NPN transistor is polarized in this way, a small current entering the base makes it possible for a much larger current to flow from the collector to the emitter. This ability to control a larger current with a smaller one is the key to its amplifying or switching functions.

#### 4.2.2 Polarizing a PNP transistor

- **Base-emitter junction:** Like with the NPN, the base-emitter junction must be forward-biased, but in a PNP transistor, the base is made slightly negative relative to the emitter. This allows positive charge carriers, called holes, to move from the emitter (P-type) to the base (N-type).

- **Collector-base junction:** This junction is reverse-biased by applying a more negative voltage to the collector compared to the base. This reverse bias facilitates the flow of current from the emitter to the collector.

**In action:** When a PNP transistor is polarized correctly, a small current flowing out of the base enables a larger current to pass from the emitter to the collector, allowing it to control a larger current with a smaller one just as with the NPN.

### 4.3 Study of the transistor's currents

The relationships between the currents in a Bipolar Junction Transistor are fundamental to understanding its operation. These are based on the three main currents in a transistor: the base current ( $I_B$ ), the collector current ( $I_C$ ), and the emitter current ( $I_E$ ). In the following, we discuss the primary relationships:

#### a. Basic Relationship

At its core, a transistor follows the principle of current conservation: the total current entering equals the total current leaving. This means:

$$I_E = I_C + I_B \quad (4.1)$$

This relationship holds true for all modes of operation.

### b. Collector current and gain

When the transistor is in its active mode (used for amplification), the collector current depends on the base current and a factor called the current gain ( $\beta$ ):

$$I_C = \beta I_B \quad (4.2)$$

Where,  $\beta$  is the transistor's current gain, usually a large number (e.g. 100-300). So, a small base current is "multiplied" by  $\beta$  to produce a larger collector current. This is what makes BJTs effective as amplifiers.

### c. Emitter current and total gain

The emitter current can also be expressed in terms of the base current and the transistor's total gain ( $\alpha$ ), where  $\alpha$  is related to  $\beta$  as follow:

$$\alpha = \frac{\beta}{1+\beta} \quad (4.4)$$

Using this relationship, the emitter current can be written as:

$$I_E = (1 + \beta)I_B \quad (4.5)$$

This shows that the emitter current is slightly larger than the collector current due to the additional base current.

### d. Saturation currents (leakages)

Leakage current, in the context of electrical systems and circuits, refers to the small amount of current that flows through a circuit even when it is not supposed to be active or when a device is turned off. This can happen for various reasons, depending on the system. In a transistor, even when it is in the "cutoff" state (off mode), there may still be a minimal current flowing between the collector and emitter due to leakage in the base-emitter junction or imperfections. This residual current is very small but can affect sensitive circuits, especially in low-power devices.

Even when a transistor is "off" or in cutoff mode, small leakage currents can flow:

- ✓  **$I_{CB0}$** : The saturation current of the collector-base junction when  $I_E=0$  (in the case of a common-base configuration).

- ✓  **$I_{EB0}$** : The saturation current of the emitter-base junction when  $I_C=0$  (in the case of a common-collector configuration).

- ✓  **$I_{CEO}$** : The saturation current of the collector-emitter junction when  $I_B=0$  (in the case of a common-emitter configuration).

These currents are usually very small but can still be important in precision or low-power circuits.

- **Common-base configuration :**  $I_C = \alpha I_E + I_{CB0}$

- **Common-emitter configuration :**  $I_C = \beta I_B + I_{CEO}$

- **Common-collector configuration :**  $I_E = \gamma I_B + I_{EB0}$

At low temperature the leakage currents are zero.

$$\alpha = \frac{I_C}{I_E}, \beta = \frac{I_C}{I_B} \text{ and } \gamma = \frac{I_E}{I_B} \quad (4.6)$$

Where:  $\alpha < 1$ ,  $\beta \gg 1$  and  $\gamma \gg 1$

$$\alpha = \frac{\beta}{1+\beta}, \beta = \frac{\alpha}{1-\alpha}, \gamma = 1 + \beta = \frac{1}{1-\alpha}$$

Subsequently, we can deduce:

$$I_{CE} = (1 + \beta) I_{CB} \quad (4.7)$$

**Remark:** When the temperature increases by **5°C**, the residual currents increase by **one unit**.

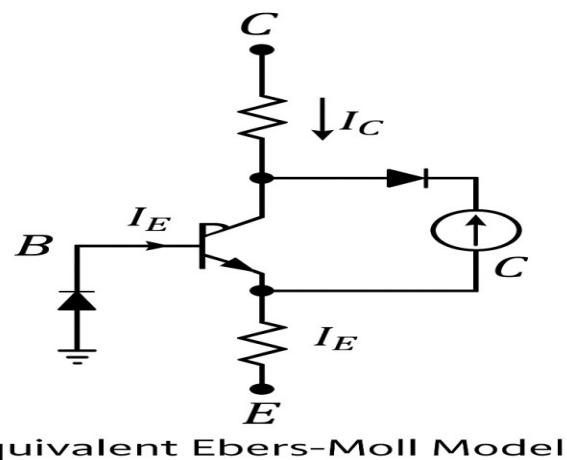

#### 4.4 Ebers-Moll model

The Ebers-Moll model provides a comprehensive mathematical representation of a bipolar junction transistor by considering it as two coupled diodes with controlled current flow. The model accurately describes the behavior of the BJT in all its regions of operation (active, saturation, and cutoff). Below a detailed explanation and demonstration.

For an NPN transistor, the Ebers-Moll model defines the emitter and collector currents as:

$$I_E = [I_{ES} \exp\left(\frac{V_{BE}}{V_T}\right) - 1] - [\alpha_R I_{CS} \exp\left(\frac{V_{BC}}{V_T}\right) - 1] \quad (4.8)$$

$$I_C = [\alpha_F I_{ES} \exp\left(\frac{V_{BE}}{V_T}\right) - 1] - [I_{CS} \exp\left(\frac{V_{BC}}{V_T}\right) - 1] \quad (4.9)$$

$$I_B = I_E - I_C \quad (4.10)$$

Where:

- $I_{ES}$ ,  $I_{CS}$ : Reverse saturation currents of emitter-base and collector-base diodes

- $V_{BE}$ ,  $V_{BC}$ : Base-emitter and base-collector voltages

- $V_T$ : Thermal voltage ( $\sim 25.85$  mV at room temperature)

- $\alpha_F$ : Common-base forward current gain (typically  $\sim 0.99$ )

- $\alpha_R$ : Common-base reverse current gain (typically  $\sim 0.5$ – $0.8$ )

The equivalent circuit includes two diodes (base-emitter and base-collector) and two current sources representing  $\alpha_F I_E$  and  $\alpha_R I_C$ . This allows modeling of both injection and recombination effects.

**Figure 4.3:** Equivalent Ebers-Moll model circuit diagram.

#### 4.5 Modes of operation

Typical BJT operating regions are described by junction biases as follows:

- Active Mode:  $V_{BE} > 0, V_{BC} < 0$

- Saturation Mode:  $V_{BE} > 0, V_{BC} > 0$

- Cut-off Mode:  $V_{BE} < 0, V_{BC} < 0$

- Reverse Active:  $V_{BE} < 0, V_{BC} > 0$

The model supports all transistor operation modes including cutoff, forward active, saturation, and reverse active. These are defined based on the biasing of  $V_{BE}$  and  $V_{BC}$ . In forward active mode, the model simplifies to:

$$I_c = \beta I_B = \alpha_R I_c \approx \beta I_B = \alpha_F I_E \quad (4.11)$$

The emitter current follows:

$$I_E = [I_{ES} \exp\left(\frac{V_{BE}}{V_T}\right) - 1] \quad \text{and} \quad \beta = \frac{\alpha_F}{1 - \alpha_F} \quad (4.12)$$

Applications of Ebers-Moll model include circuit simulations, nonlinear dc analysis, and spice modeling. Limitations include the lack of high-frequency effects and parasitic modeling, which are covered by advanced models like Gummel-Poon.

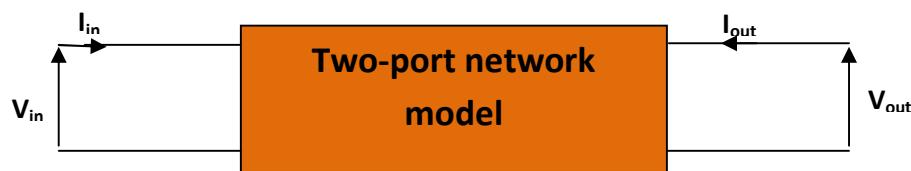

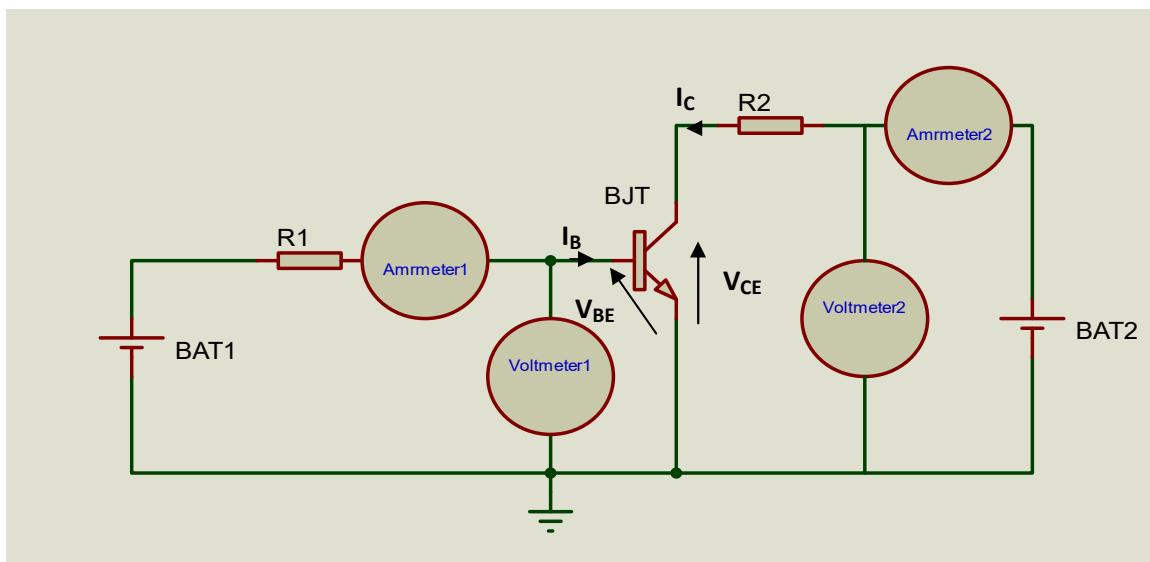

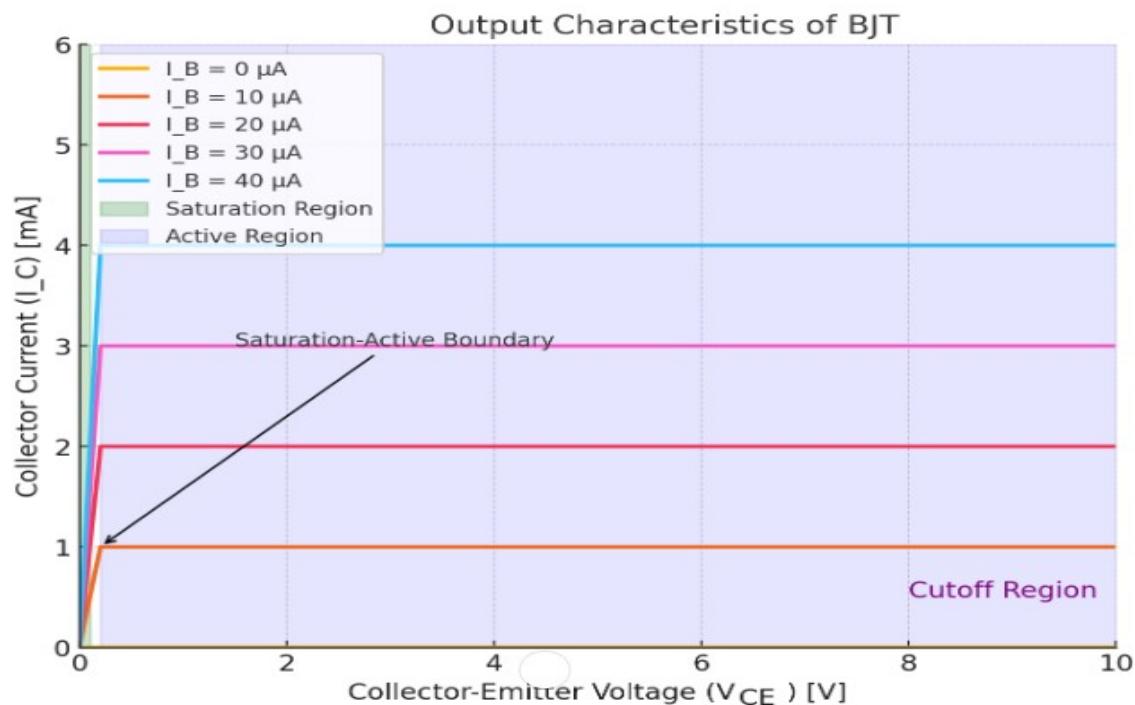

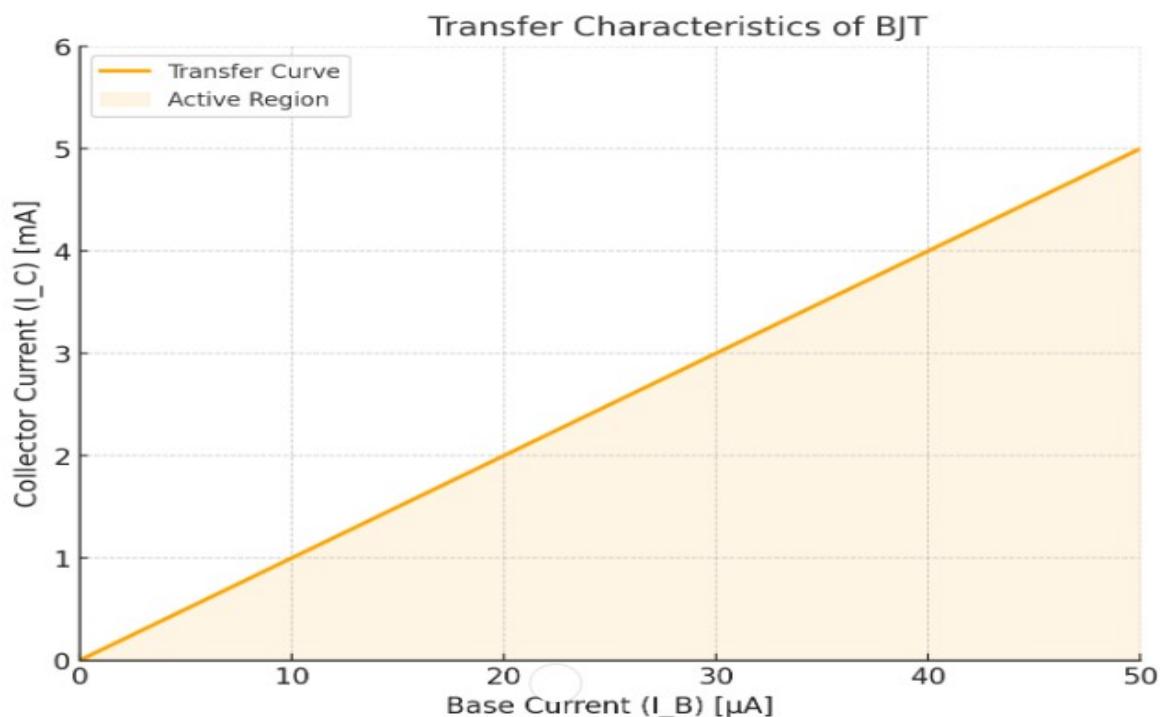

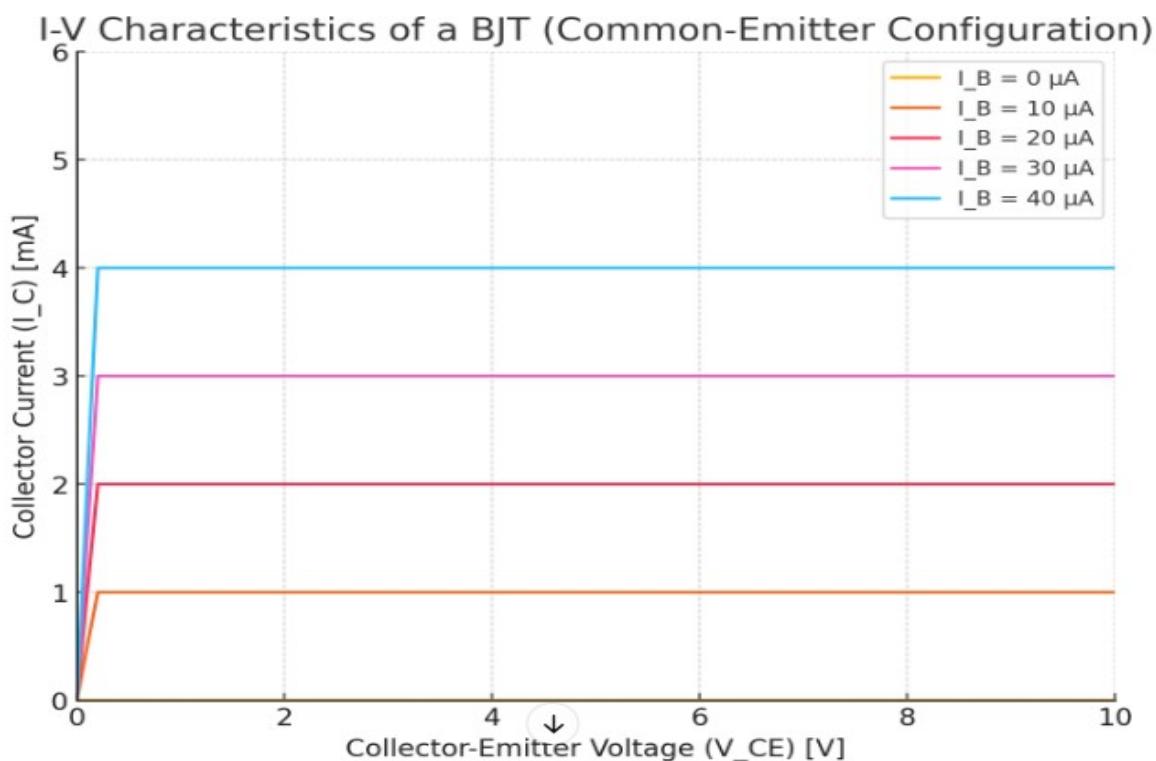

#### 4.5.1 Current-voltage characteristics

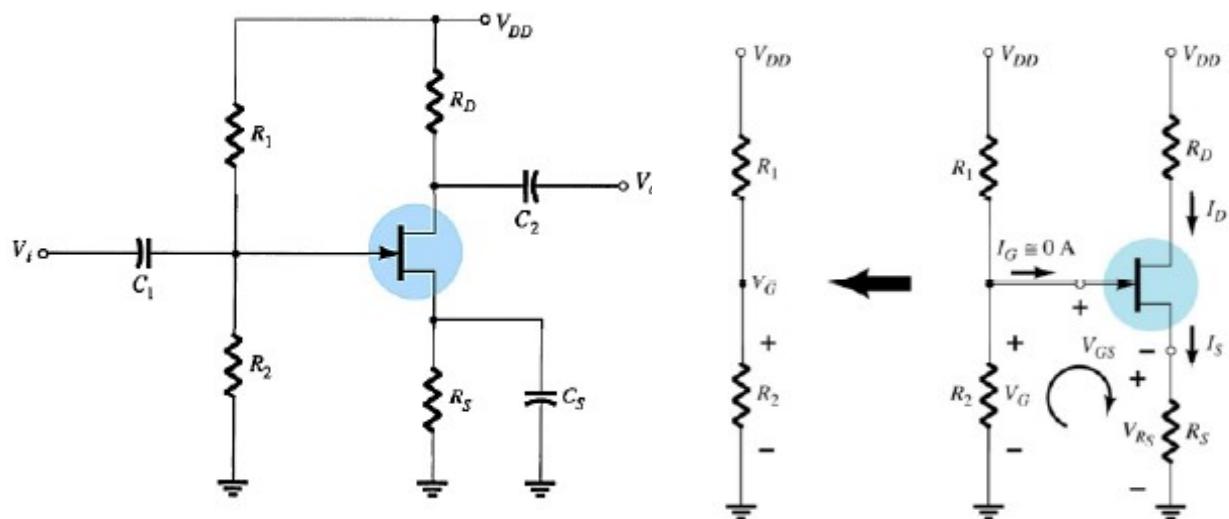

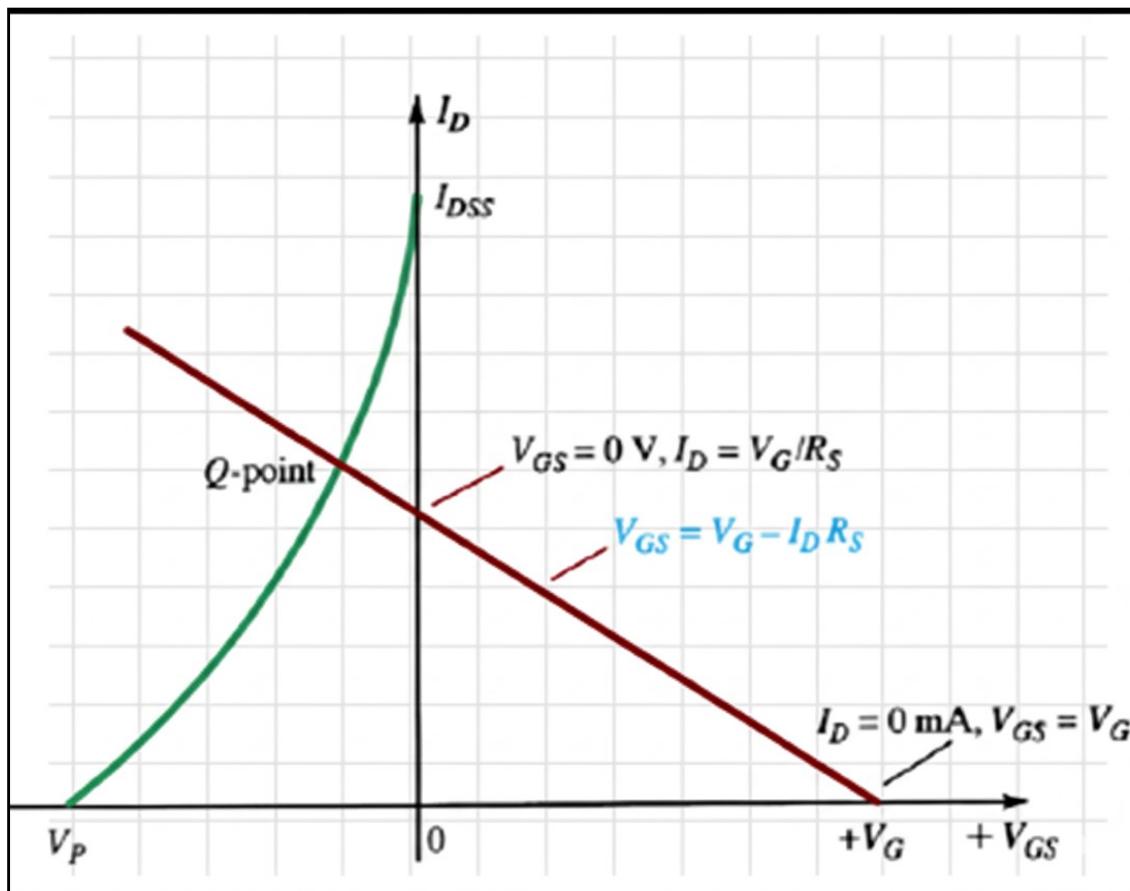

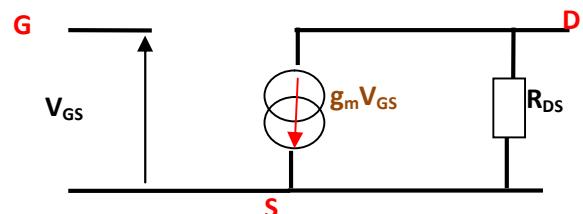

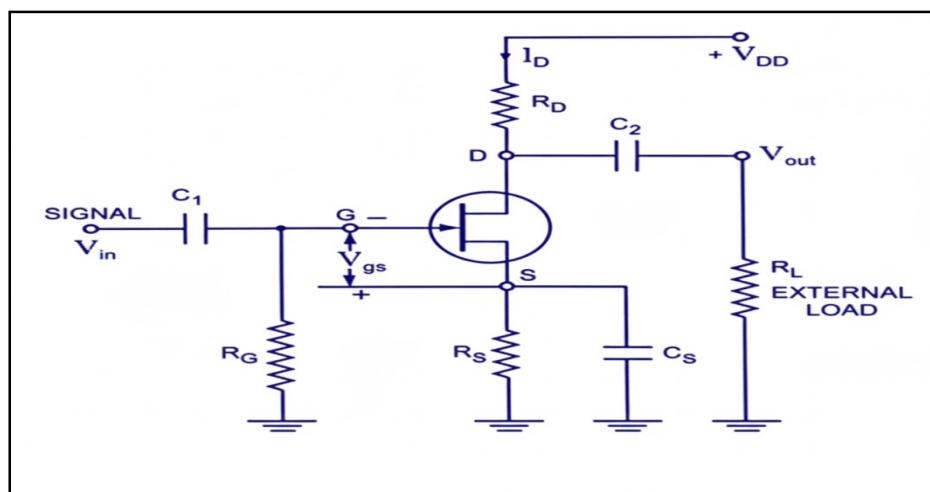

The current-voltage (I-V) characteristics of a BJT represent the relationship between the current flowing through the transistor and the voltage applied across its terminals. When a small current is applied to the base, it controls the larger current flowing from the emitter to the collector. The current-voltage characteristics are crucial for understanding how it operates in a circuit. These characteristics also help to visualize and understand how a BJT behaves under different operating conditions. Furthermore, the I-V characteristic curve helps engineers design circuits by indicating the operating points of a BJT, showing regions of amplification, saturation, and cutoff, which are vital for applications like amplification, switching, and signal modulation. We can study these characteristics by considering the transistor as a two-port network model and hybrid parameters (**h-parameters**).